2. PCI Interface

39

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

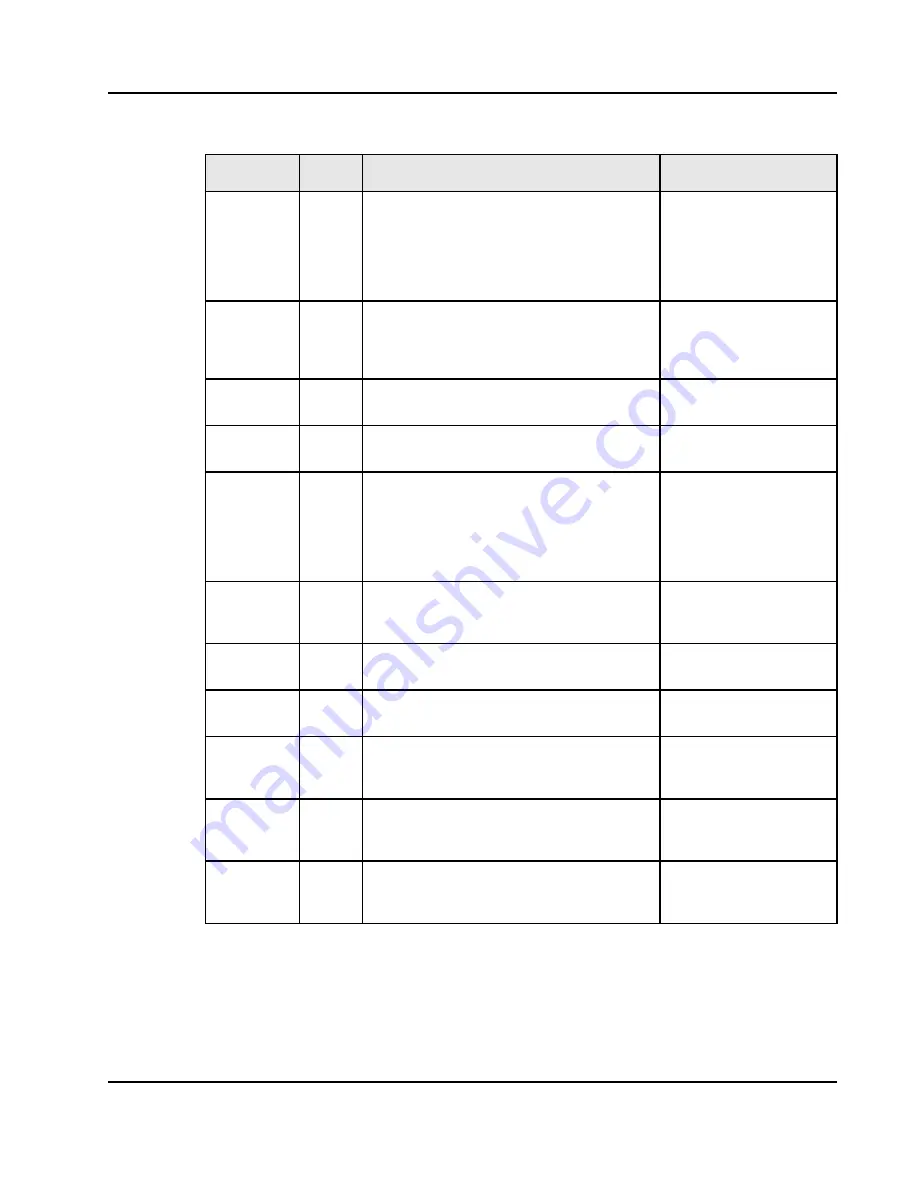

BAR_EN

R/W

Enables the PCI Base Address register. When this

bit is set, the Px_BSTx Register is R/W and visible

to Processor Bus access and PCI memory cycles.

When this bit is cleared, the Px_BSTx register

returns only zeros on a read. Writes will have no

effect on Px_BSTx when this bit is cleared.

Enabled or configurable

through EEPROM

BS[3:0]

R/W

Sets the block size of the PCI target image. The

size of the image is 64Kbyte * 2

BS

.

Default value is 0, can be

programmed through any

port after reset or loaded

through EEPROM.

MODE

R/W

Maps the incoming PCI transaction to either

memory or I/O space on the alternate PCI bus.

Default value is 0 (Memory

command generation)

DEST

R/W

Directs the incoming PCI transaction to either the

processor bus or the alternate PCI interface.

Defaults to processor bus

MEM_IO

R/W

Commands to the corresponding image generates

Memory Read commands on the destination PCI

bus (Py) with the same byte enables latched from

the source bus transaction PowerSpan II is

capable of performing 1,2,3, or 4 byte memory

transfers on the PCI bus(es).

Default value is 0 (Regular

I/O mode)

RTT[4:0]

R/W

A 5-bit value, defined in the processor bus

protocol, is generated on the PB_TT lines during a

read on the processor bus.

Defaults to Read

GBL

R/W

Controls the assertion of the PB_GBL_ cache

control signal.

Asserts PB_GBL_

CI_

R/W

Controls the assertion of the PB_CI_ cache

control signal.

Asserts PB_CI_

WTT[4:0]

R/W

A 5-bit value, defined in the processor bus

protocol, is generated on the PB_TT lines during a

write on the processor bus.

Defaults to Write with Flush

PRKEEP

R/W

Enables PowerSpan II to keep prefetch read data

over subsequent transactions (see

Disabled

END[1:0]

R/W

Sets endian mapping to little-endian, PowerPC

little-endian, or big-endian (see

Big-endian is the default

mode.

Table 5: Programming Model for PCI Target Image Control Register

Bits

Type

Description

Default Setting