2. PCI Interface

65

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

The Inbound MFAs are 32-bit offsets from the translated PowerSpan II I

2

0 target image window base

address in local IOP memory. When the Host platform or an external IOP wishes to send a message to

the local IOP it must first obtain an MFA from the Inbound Free List. The external platform is then free

to place a message in the associated MF. The MFA is then placed into the Inbound Post List for the

Local IOP to process.

2.6.3.3

Outbound Queue

The Outbound Queue Register is the messaging interface used by the local IOP to post messages to the

Host. The I

2

O Outbound Queue Register Interface is located at offset 0x044 of the PowerSpan II PCI

I

2

O target image in PCI memory space. The Outbound Queue has a Free List FIFO and a Post List

FIFO, both of which reside in the IOP local memory. The Free List contains the Message Frame

Address (MFAs) of Message Frames (MFs) in the Host system memory, which are available to the

local IOP for writing outbound messages. Outbound MFAs are absolute addresses of a Message Frame

in Host memory. The Post List contains the MFAs of MFs in the Host system memory which contain

outbound messages for the Host to process. When the local IOP wishes to send a message to the Host

platform it must first obtain an MFA from the Outbound Free List. The local IOP is then free to place a

message in the associated MF. The MFA is then placed into the Outbound Post List for the Host to

process. All Outbound messages are targeted for the Host platform. If the local IOP wishes to send a

message to another IOP (peer-to-peer communication) it uses the external IOPs Inbound Queue to post

the Message.

2.6.3.4

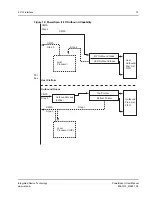

Protocol for Exchanging Messages

PowerSpan II I

2

O Registers

The PowerSpan II PCI I

2

O Shell Interface implements the following I

2

O defined registers:

•

I

2

O Outbound Post List Interrupt Status Register

•

I

2

O Outbound Post List Interrupt Mask Register

•

I

2

O Inbound Queue

•

I

2

O Outbound Queue

•

I

2

O Host Outbound Index Register (used for Outbound Option)

In addition to the registers defined in the

I

2

O 2.0 Specification

, PowerSpan II implements a number of

registers to support the I

2

O message passing protocol of the Shell Interface.

•

PCI I

2

O Target Image Control Register (PCI_TI2O_ CTL)

•

PCI I

2

O Target Image Translation Address Register (PCI_TI2O_ TADDR)

•

I

2

O Queue Base Address Register (I20_ QUEUE_BS)

All I

2

O Inbound Queue MFAs must be offsets of greater than 4 Kbytes.