2. PCI Interface

63

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

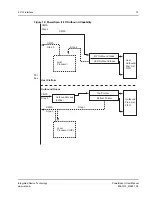

2.6.2

IOP Functionality

A number of configuration steps are required before PowerSpan II and the embedded processor bus are

enabled to provide IOP functionality. The following example assumes PCI-1 is the Primary PCI

Interface.

The steps required to implement IOP functionality are listed below.

1.

In order to identify PowerSpan II as an I

2

O Controller the

“PCI-1 Class Register” on page 254

must be programmed as follows:

— Base Class Code (BASE) = 0x0E

— Sub Class Code (SUB) = 0x00

— Programming Interface (PROG) = 0x01

2.

The Inbound and Outbound Queues’ location and size in IOP memory must be programmed in

PowerSpan II. This is accomplished by programming the

“I2O Queue Base Address Register” on

— Processor Bus I

2

O Base Address (PB_I2O_BS): specifies base address of the Queues

— FIFO Size (FIFO_SIZE): specifies the size of the Queues

3.

The PCI I

2

O target image must be configured to claim I

2

O Shell and Message Frame accesses from

PCI. The following registers must be programmed:

— Configure I

2

O image size with the Block size (BS) bit in

(PCI_TI2O_CTL).

— Enable Base Address Register (BAR) visibility in configuration space.

–

Set BAR_EN in the PCI_TI2O_CTL register.

— Program PCI Base Address Register

“PCI-1 I2O Target Image Base Address Register” on

.

–

Set Image Enable (IMG_EN) in

“PCI I2O Target Image Control Register” on page 352

enable decode. Note that this occurs if a non-zero value is written to the PCI Base

Address Register.

— Configure Processor Bus Master transaction parameters.

–

Write Transfer Type (WTT) in the PCI_TI2O_CTL register.

–

Read Transfer Type (RTT) in the PCI_TI2O_CTL register.

–

Global Command (GBL) in the PCI_TI2O_CTL register.

–

Cache Inhibit (CI) in the PCI_TI2O_CTL register.

— Select endian conversion mechanism with the Endian Conversion (END) bit in the

PCI_TI2O_CTL register

Programming values other than the ones listed above do not affect the behavior

of PowerSpan II as an I2O device

.