2. PCI Interface

70

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

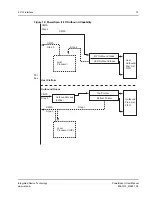

Once the Host processor has processed the MFA, it writes the MFA back to the Outbound Queue

Register (0x044) to place it back in the Outbound Free List FIFO. PowerSpan II accepts the write

transaction and takes responsibility for replacing the MFA in the Outbound Free List FIFO at the

address pointed to by the Outbound Free List Top Pointer Register. PowerSpan II then increments the

Outbound Free List Top Pointer Register by four.

2.6.6

Pull Capability

The

I

2

O 2.0 Specification

defines an enhancement that allows the IOP to provide a capability to pull

the I

2

O Inbound messages from the Host memory. In this configuration the Host places the I

2

O

Inbound messages in MFs located in the Host memory as opposed to the IOP local memory. The Host

must also implement a Host Free List FIFO in Host memory. This FIFO does not replace the IOP

Inbound Free List FIFO, which must still be implemented in the IOP local memory to support normal

inbound message passing, or peer to-peer message passing. This capability increases server

performance by virtue of the Host CPU and server platforms being optimized for memory access rather

than I/O access. Under this option, the Host can post Inbound messages to the IOP with a single write

to the IOP. The IOP pulls the MF from the Host memory and releases a MF to the Host by generating a

single write to Host memory. The Pull capability applies only to the IOP’s Inbound Queue and to the

posting of messages by the Host.

The Pull model requires 16 byte alignment of the message frames, therefore, the least significant four

bits of the MFA are always zero. The Pull options use these four bits to create an Extended MFA

(XMFA). The Pull model uses the least significant bit of the XMFA to indicate a pull request. This bit

is the Pull Indicator or the P bit. Bits 3:1 of the XMFA indicate the number of data transfers required to

copy the message. This number is system specific and has no effect on the PowerSpan II’s behavior.

To prevent overflow of the local Inbound Post List FIFO the IOP reports an Inbound Post List

Headroom to the Host, which is the difference between the size of the Inbound Post List FIFO and the

total number of IOP Inbound Message Frames allocated by the IOP in local memory. This is the

number of XMFAs the Host can Post to the I

2

O Inbound Post List FIFO and guarantee not to overflow

the Inbound Post List FIFO. The IOP must not allocate more MFAs in the Inbound Free List than can

be accepted in the Inbound Post List (along with XMFAs) without causing overflow.

Equation

•

#Inbound Free MFAs + #XMFAs <= FIFO_SIZE (see

“I2O Queue Base Address Register” on

2.6.6.1

Host Posting

The Host can post a message to the IOP using the Pull Capability by using the following methods:

•

reading an XMFA from the Host Free List FIFO

•

writing an Inbound Message to the MF in Host memory indicated by the XMFA

•

writing an XMFA to the Inbound Queue Register at offset 0x040 of the I

2

O target image on PCI

The XMFA is processed by the PowerSpan II in the same way as a normal MFA posted to the local IOP

by the Host or external IOP. The IOP can determine if the XMFA is posted using the Pull Capability

and to pull the message from the system memory. To release an XMFA back to the Host platform the

IOP writes the XMFA back to the Host Free List FIFO which resides in system memory.