3. Processor Bus Interface

89

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

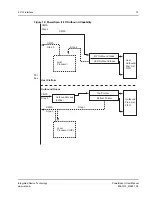

3.3.1.3

Address Tenure

Each slave on the PB Interface is responsible for the following:

•

decoding the address broadcast by the master

•

claiming the address tenure with PB_AACK_ assertion

•

managing the data termination signals during the data tenure

The PB Slave uses PB_AACK_ to limit the level of address pipelining to one. The earliest the PB slave

can assert PB_AACK_ is two clocks after PB_TS_.

The PB Slave does not acknowledge subsequent address phases until it finishes its participation in the

current data tenure. If the previous address phase was claimed by another slave, the PB slave does not

acknowledge the current address phase until the previous slave completes its data tenure.

The use of PB_ARTRY_ by the PB Slave is enabled by the Address Retry Enable (ARTRY_EN) bit in

the

“Processor Bus Miscellaneous Control and Status Register” on page 304

. If the ARTRY_EN bit is

set to 0, the PB_ARTRY_ signal is not asserted and the PB slave retains ownership of the bus. The PB

Slave retains ownership after the assertion of PB_AACK_ and until it is able to assert PB_TA.

When ARTRY_EN has a value of 1, the PB Slave can assert PB_ARTRY_. The default setting is 0

(ARTRY_EN is disabled). The PB Interface has higher performance if the ARTRY_EN bit is enabled.

PowerSpan II’s PB Master or another external master can gain access to the bus when PowerSpan II

cannot assert PB_TA.

When ARTRY_EN is enabled, the PB Slave asserts PB_ARTRY_ in the following situations:

•

a write destined for PCI cannot be internally buffered

•

when a read request has been latched and read data is being fetched from PCI

•

a register access when a load from EEPROM is in progress

•

writing to registers when another bus (PCI-1, PCI-2) is also writing to the register block

If the assertion of PB_ARTRY_ is enabled, it occurs the clock after PB_AACK_ within the

address

retry window

.

3.3.1.4

Address Translation

The incoming address on the PB Interface can have a translation offset applied to it using the

TADDR[19:0] field of the

“Processor Bus Slave Image x Translation Address Register” on page 292

When the translation offset is applied to the incoming PB address, the translated address appears on the

destination bus (PCI-1 or PCI-2). The translation offset replaces the PB address, up to the size of the

image. TADDR[19:0] replaces PB address lines PB_A[0:19].