2. PCI Interface

73

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

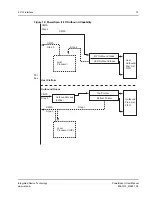

2.6.7

Outbound Option

The

I

2

O 2.0 Specification

allows for the IOP to provide an enhanced capability to post reply messages

to the Host. This mechanism is independent of the Pull Capability of the previous section. This

capability reduces the number of reads that the Host must perform to the IOP. Under the Outbound

Option Operation, the local IOP copies out the reply message to the Host system memory and then

posts the message by performing a single write to the Host memory. The Host need only to write to the

PowerSpan II to return the MFA.

The Outbound option requires 16-byte alignment of the message frames and thus the least significant

four bits of the MFA are always zero. The Outbound option uses these four bits to create and Extended

MFA (XMFA). The least significant bit of the outbound XMFA is the Cycle Indicator bit or the C bit.

2.6.7.1

Host Posting

To post a message to the Host, the IOP completes the following:

1.

Obtains an Outbound MFA from the Outbound Free List FIFO.

2.

Copies out the reply message to the MF indicated by the Host allocated Outbound MFA.

3.

Posts the Outbound MFA to the HostPostList FIFO pointed to by the IOP Outbound Index

Register, setting the least significant bit of the MFA to 1, and increment the IOP Outbound Index

Register by writing to the IOP Outbound Index Increment Register.

The PowerSpan II IOP Outbound Index Register is initialized by the IOP with a value received along

with the Host Outbound Post List FIFO Size through an “IOP Message Outbound Extensions” message

from the Host. The size of the Host Outbound Post List FIFO is specified in the HOPL_SIZE bit in the

I2O_CSR register.

The PowerSpan II IOP Outbound Index Register points to the Top of the Host Outbound Post List

FIFO implemented in Host memory. When it reaches the end of the FIFO the IOP resets the IOP

Outbound Index Register to the base of the FIFO. The IOP writes XMFAs to the FIFO with the C bit

set to 0, and continues to alternate this pattern. This allows the Host to determine where the IOP

processor has last written to the FIFO.

PowerSpan II also implements a Host Outbound Index Register where the Host will write its Host

Outbound Post List FIFO Index after servicing Outbound reply messages posted using the Outbound

Option. The Host Outbound Index Register points to the Bottom of the Host Outbound Post List FIFO.

PowerSpan II maps this register into the PowerSpan II I

2

O Target Image Shell Interface at the offset

specified in the I

2

O Host Outbound Index Offset Register. This register is initialized by the IOP with

an offset provided by the Host through the IOP Message Outbound Extensions message.

When I

2

O Extended capabilities are enabled with I2O_CSR[XI2O_EN], PowerSpan II will set an

interrupt status bit in the I

2

O Outbound Post List Interrupt Status register when the I

2

O Host Outbound

Index Register is not equal to the I

2

O IOP Outbound Index Register. This indicates that the Host

Outbound Post List FIFO is non-empty.