2. PCI Interface

51

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

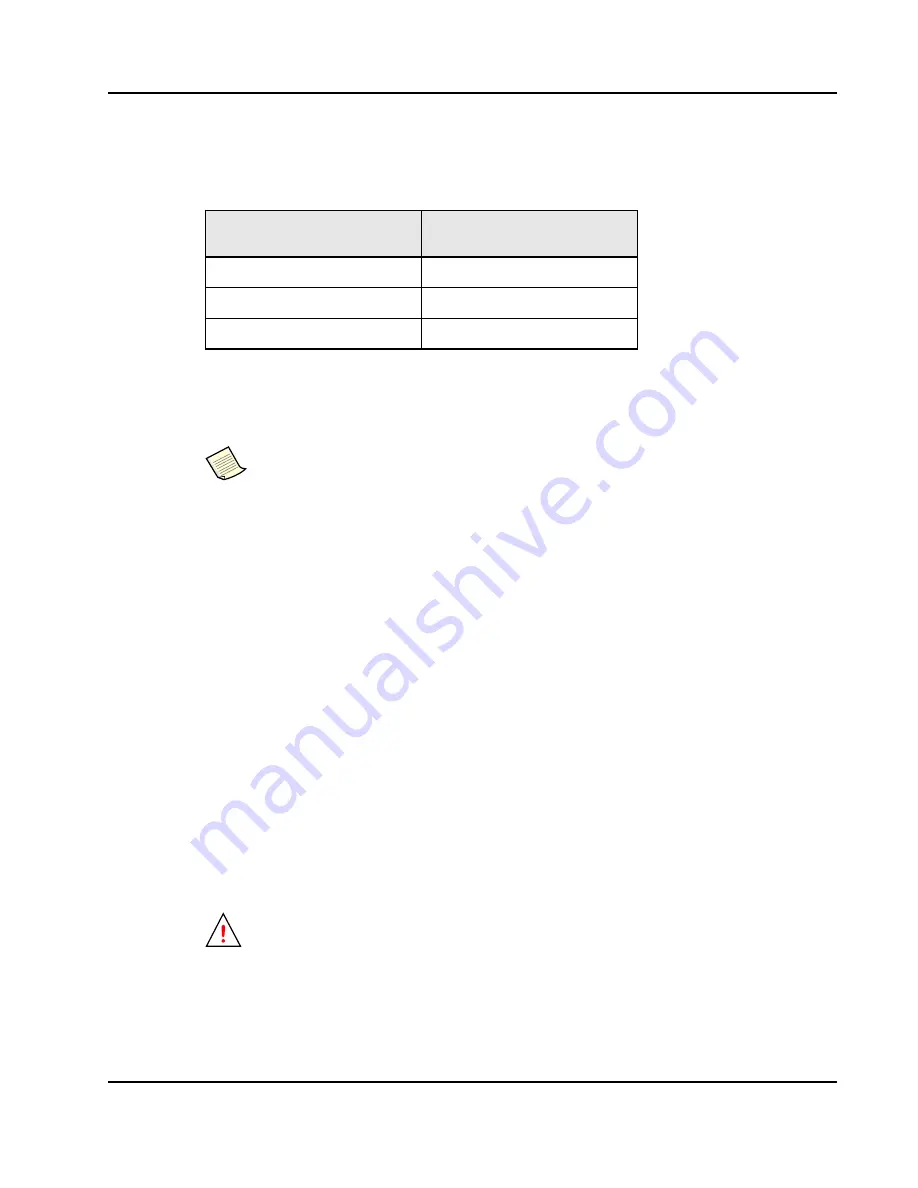

The PowerSpan II PCI Master generates a Memory Read command selection according to the rules in

The read amount presented to the PCI Master determines the command used. A Memory Read Line

command uses the burst length programmed into the CLINE[7:0] field in the

. It is programmable to 16-, 32-, 64-, or 128 bytes.

2.3.3.3

Parity Monitoring and Generation

PowerSpan II monitors Px_PAR#/Px_PAR64# when it accepts data as a PCI master during a read, and

drives Px_PAR#/Px_PAR64# when it provides data as a PCI master during a write. PowerSpan II also

drives Px_PAR#/Px_PAR64# during the address phase of a transaction when it is a PCI master. In both

address and data phases, the Px_PAR#/Px_PAR64# signal provides even parity for Px_C/BE#[3:0] and

Px_AD[31:0]. Even parity is enabled Px_C/BE#[7:4] and Px_AD[63:32] for PCI-1 in 64-bit mode.

PowerSpan II parity response is enabled through the Parity Error Response (PERESP) bit in the

Control and Status Register.” on page 251

. Data parity errors are reported through the assertion of

Px_PERR# when the PERESP bit is set. The Detected Parity Error (D_PE) bit in the

and Status Register.” on page 251

is set when PowerSpan II encounters a parity error as a PCI master

on any transaction. PowerSpan II records an error condition in the event of a parity error (see

).

The Master Data Parity Detected (MDP_D) bit in the

“PCI-1 Control and Status Register.” on page 251

is set if the PERESP bit is enabled and either PowerSpan II is the master of the transaction where it

asserts PERR#, or the addressed target asserts PERR#. If the transfer originated from the Processor

Interface, then PowerSpan II sets the MDP_D bit and the Px_PB_ERR_EN bit in the

. PowerSpan II then asserts an interrupt (see

).

Table 9: PowerSpan II PCI Master Read Commands

Internal Request of Transaction

Length

PCI Memory Read Command

<= 8 bytes

Memory Read

<= CLINE[7:0] in Px_MISC0

Memory Read Line

> CLINE[7:0] in Px_MISC0

Memory Read Multiple

If the PCI Master does not complete the burst read transaction before a target termination, it

completes the read with subsequent PCI read transactions at the appropriate address.

PowerSpan II continues with the transaction independent of any parity errors reported during

the transaction.