2. PCI Interface

69

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

2.6.5

Outbound Messages

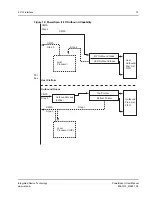

The Outbound Free and Post List FIFOs are implemented as circular queues using Bottom and Top

pointers. PowerSpan II implements the Bottom and Top pointers for the Outbound Free List FIFO and

the Outbound Post List FIFO.

When the local IOP wants to post a message to the Host, it must first acquire an MFA from the

Outbound Free List. The IOP reads the MFA pointed to by the Outbound Free List Bottom Pointer

Register. The processor then increments the Outbound Free List Bottom Pointer Register by four to

point to the next entry of the FIFO.

The IOP, having obtained a Host MFA, is then free to write a message through the PowerSpan II to the

Host MF at the Host memory address specified by the MFA. Once the message is transferred, the IOP

writes the MFA to the Outbound Post List FIFO at the address pointed to by the Outbound Post List

Top pointer maintained by PowerSpan II. The processor then increments the Outbound Post List Top

Pointer Register by four.

While the Outbound Post List FIFO is non-empty PowerSpan II sets an interrupt status bit in the

PowerSpan II I

2

O Outbound Post List Interrupt Status Register of the I

2

O target image (0x030). If the

Interrupt is not masked by the PowerSpan II Outbound Post List Interrupt Mask Register of the I

2

O

target image (0x034), PowerSpan II drives an interrupt to notify the Host processor of MFAs in the

Outbound Post list FIFO. PowerSpan II determines the Outbound Post List FIFO to be non-empty

when the Outbound Post List FIFO Bottom and Top pointers do not point to the same FIFO address.

2.6.5.1

Host Processor Functions

For Outbound Messaging, the host processor performs the following:

•

detects the interrupt.

•

reads the I

2

O Outbound Post List Interrupt Status Register (0x030).

•

reads the Outbound Queue Register at offset 0x044 of the PowerSpan II I

2

O target image map to

obtain the next Outbound Post List MFA.

•

processes the Message pointed to by the MFA.

The Outbound Interrupt Status and Mask bits are aliased in I2O_HOST in the

and I2O_HOST_MASK in the

“Interrupt Status Register 0” on page 327

. The IOP must

program I2O_HOST_MAP in the

“Interrupt Map Register Miscellaneous” on page 346

in order for the

Outbound Interrupt to be routed to PowerSpan II’s Primary PCI interrupt pin.

2.6.5.2

Outbound Message Frame Addresses (MFA)

PowerSpan II provides the MFA at the Bottom of the Outbound Post List FIFO by performing a

delayed read from the processor bus. The PowerSpan II increments the Outbound Post List Bottom

Pointer Register and compares the value with the Outbound Post List Top Pointer to determine if the

Outbound Post List FIFO is empty. When the Bottom and Top pointers contain the same value the I

2

O

Outbound Post Queue Interrupt Status bit is cleared by the PowerSpan II. Alternatively, the interrupt

can be masked out, leaving it to the Host processor to poll the Outbound Queue Register. When the

Outbound Post List FIFO is empty, the PowerSpan II returns 0xffff_ffff when the Host processor reads

the Outbound Queue Register.