7. Interrupt Handling

151

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

Interrupt Enable Register 1 enables interrupts resulting from errors occurring during the device

operation. This includes maximum retry errors, bus errors, and parity errors. A register description for

IER1 is in

The descriptions in

,

,and

groups several bits under one name. For example,

P1_x_RETRY actually corresponds to P1_P2_RETRY, P1_PB_RETRY, and P1_P1_RETRY.

For errors detected by a master, PowerSpan II has separate reporting mechanisms for each source port.

For example, if the PCI-2 master detects an address parity error on a transaction claimed by the PB

slave, the P2_PB_A_PAR bit in the ISR1 register is set.

For errors detected by a target/slave, PowerSpan II has separate reporting mechanisms for each

destination port. For example, if the PowerSpan II PB slave detects a data parity error on a transaction

destined for an agent connected to the PCI-1 external interface, the P1_PB_A_PAR bit in the ISR1

register is set.

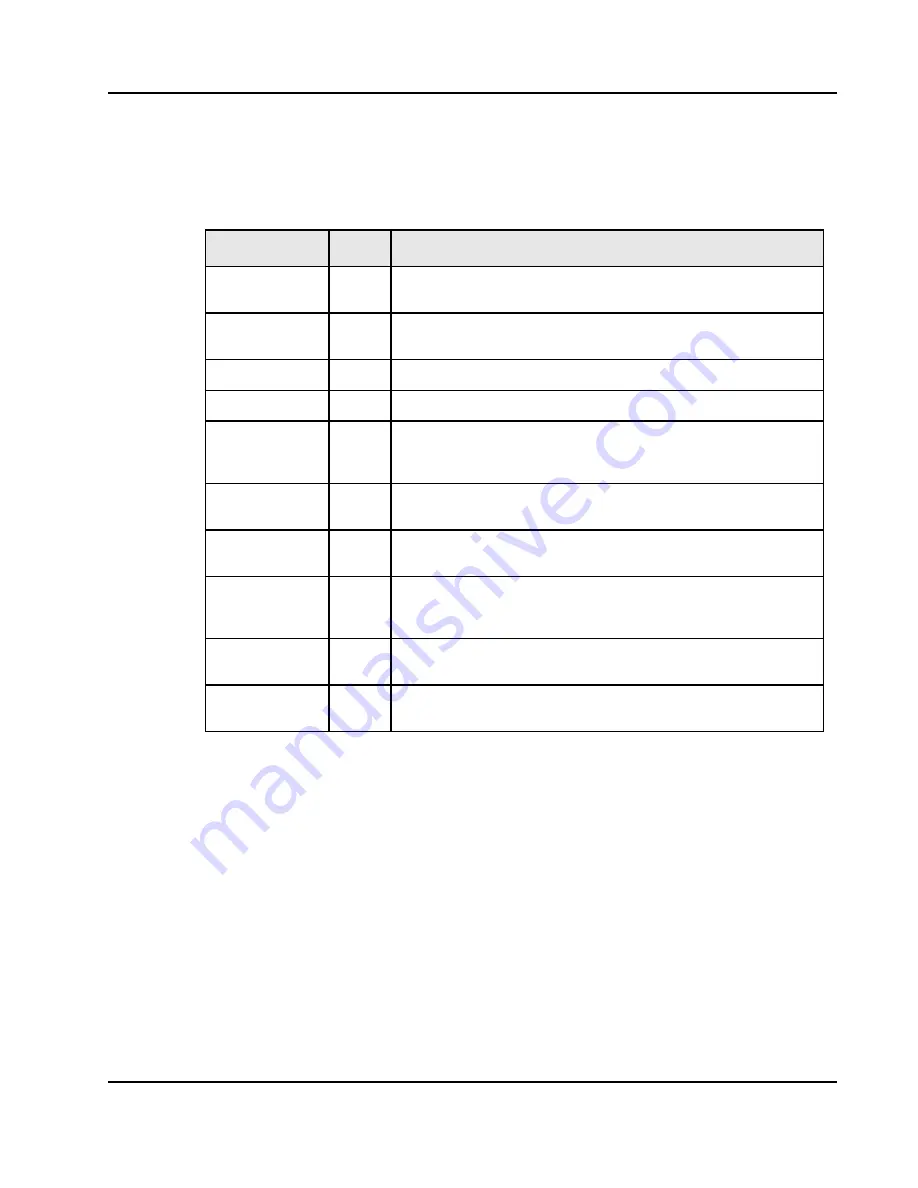

Table 37: Register Description for Interrupt Enable Register 1

Bits

Type

Description

PB_x_RETRY_EN

R/W

Enables interrupt if the PowerSpan II PB Master has detected more than

the maximum allowable retries.

PB_x_ERR_EN

R/W

Enables interrupt if the PowerSpan II PB Interface asserted (as slave) or

received (as master) PB_TEA_.

PB_A_PAR_EN

R/W

Enables interrupt if an address parity error was detected on the PB.

PB_x_D_PAR_EN

R/W

Enables interrupt if a data parity error was detected on the PB.

P2_x_ERR_EN

R/W

Enables interrupt if the PowerSpan II PCI-2 Interface detected an error.

The corresponding PCI Control and Status Register must be checked for

the error.

P2_A_PAR_EN

R/W

Enables interrupt if the PowerSpan II PCI-2 Interface detected an address

parity error.

P2_x_RETRY_EN

R/W

Enables interrupt if the PowerSpan II PCI-2 Master has detected more

than the maximum allowable retries.

P1_x_ERR_EN

R/W

Enables interrupt if the PowerSpan II PCI-1 Interface detected an error.

The corresponding PCI Control and Status Register must be checked for

the error.

P1_A_PAR_EN

R/W

Enables interrupt if the PowerSpan II PCI-1 Interface detected an address

parity error.

P1_x_RETRY_EN

R/W

Enables interrupt if the PowerSpan II PCI-1 Master has detected more

than the maximum allowable retries.