2. PCI Interface

42

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

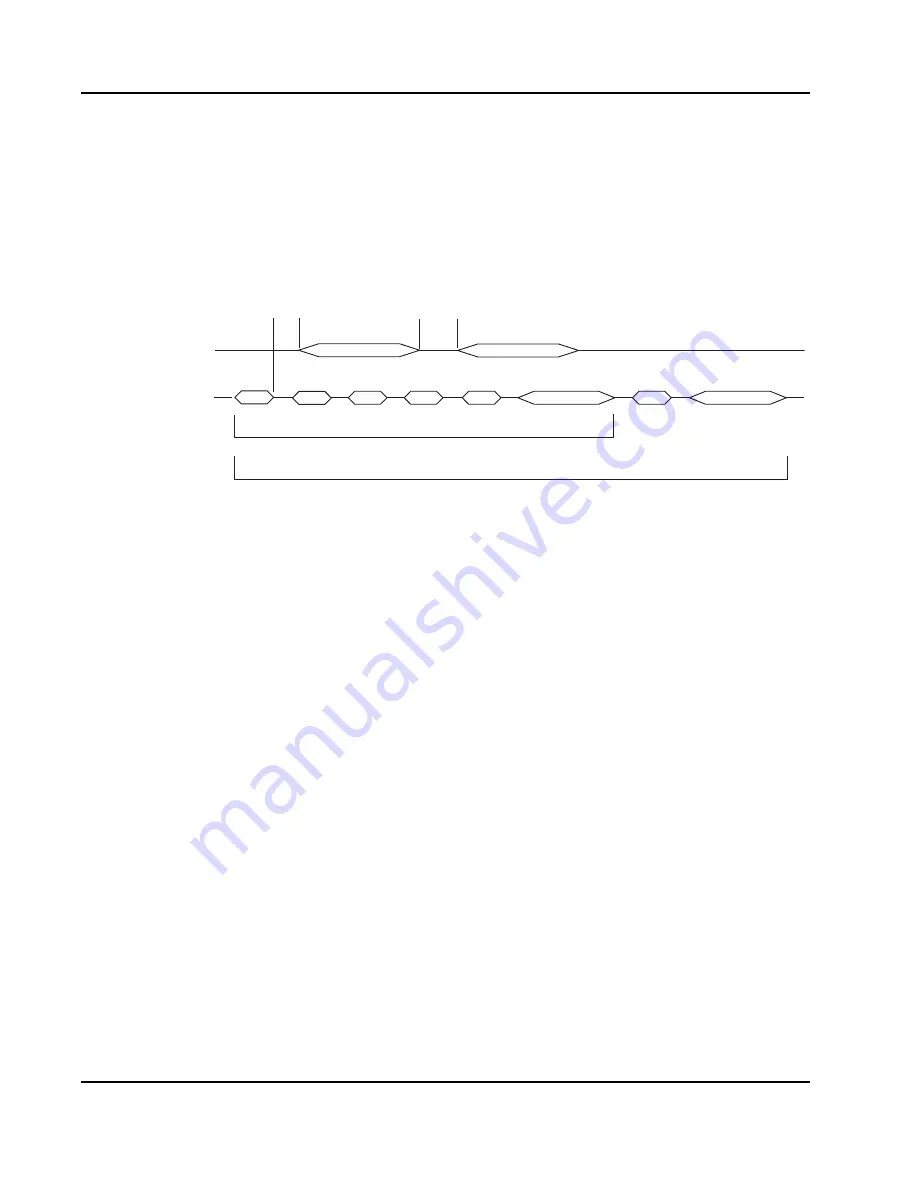

An example of PowerSpan II’s concurrent read capability is illustrated in

. The concurrent

reads in the figure are represented by Read A and Read B. In the figure, both Read A and Read B are

retried. Once Read A is completed on the processor bus, Read B is initiated on the processor bus while

the contents of Read A are returned to the PCI master. Because Read B is completed on the processor

bus while Read A data is returned to the PCI bus, read latency is significantly reduced with concurrent

reads.

Figure 6: Concurrent Read Waveform

for a general discussion of read pipelining in PowerSpan II.

Concurrent Read Phases

The delayed, concurrent reads on the PCI Target consist of the following phases:

1.

Delayed Read Request

–

The PCI Target latches the transaction parameters and issues a retry.

2.

Delayed Read

–

The PCI Target obtains the requested data. The destination bus master retries requested

data.

3.

Delayed Read Completion

–

The master repeats the transaction with the same parameters used for the initial request

and data is provided by PowerSpan II.

Read line buffers are allocated on a first come, first serve basis. When an external master makes the

initial memory request, the PowerSpan II PCI Target captures the PCI address in an available delayed

read request latch. This initiates a read on the destination bus specified by the Destination Bus (DEST)

bit in the

“PCI-1 Target Image x Control Register” on page 268

.

Prefetch Reads

All PowerSpan II PCI target memory reads are considered prefetchable to 8-byte boundaries by

default. Setting the MEM_IO bit in the

“PCI-1 Target Image x Translation Address Register” on

enables 1,2,3, or 4 byte memory reads on the PCI bus and 4 byte reads on the processor bus.

When PowerSpan II is programmed to support 4 byte transactions, only 4 byte transactions are

supported. Burst transactions are not supported while the MEM_IO bit is set to 1.

Processor Bus

PCI Bus

RET-A

RET-B

RET-A

RET-B

ACC-A

Completion-A

ACC-B

Completion-B

PPC-RDB

PPC-RDA

Device,

Arbitration and

Memory Latency

Arbitration and

Memory Latency

Single Read Latency

Double Read Latency