B1.47

Domain Access Control Register

The DACR characteristics are:

Purpose

Defines the access permission for each of the sixteen memory domains.

Usage constraints

This register is accessible as follows:

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW RW RW

RW

Configurations

DACR (NS) is architecturally mapped to AArch64 register DACR32_EL2. See

.

If EL3 is using AArch32, there are separate Secure and Non-secure instances of this register.

If EL3 is using AArch32, write access to DACR(S) is disabled when the

CP15SDISABLE2

signal is asserted HIGH.

DACR has no function when TTBCR.EAE is set to 1 to select the Long-descriptor translation

table format.

Attributes

DACR is a 32-bit register.

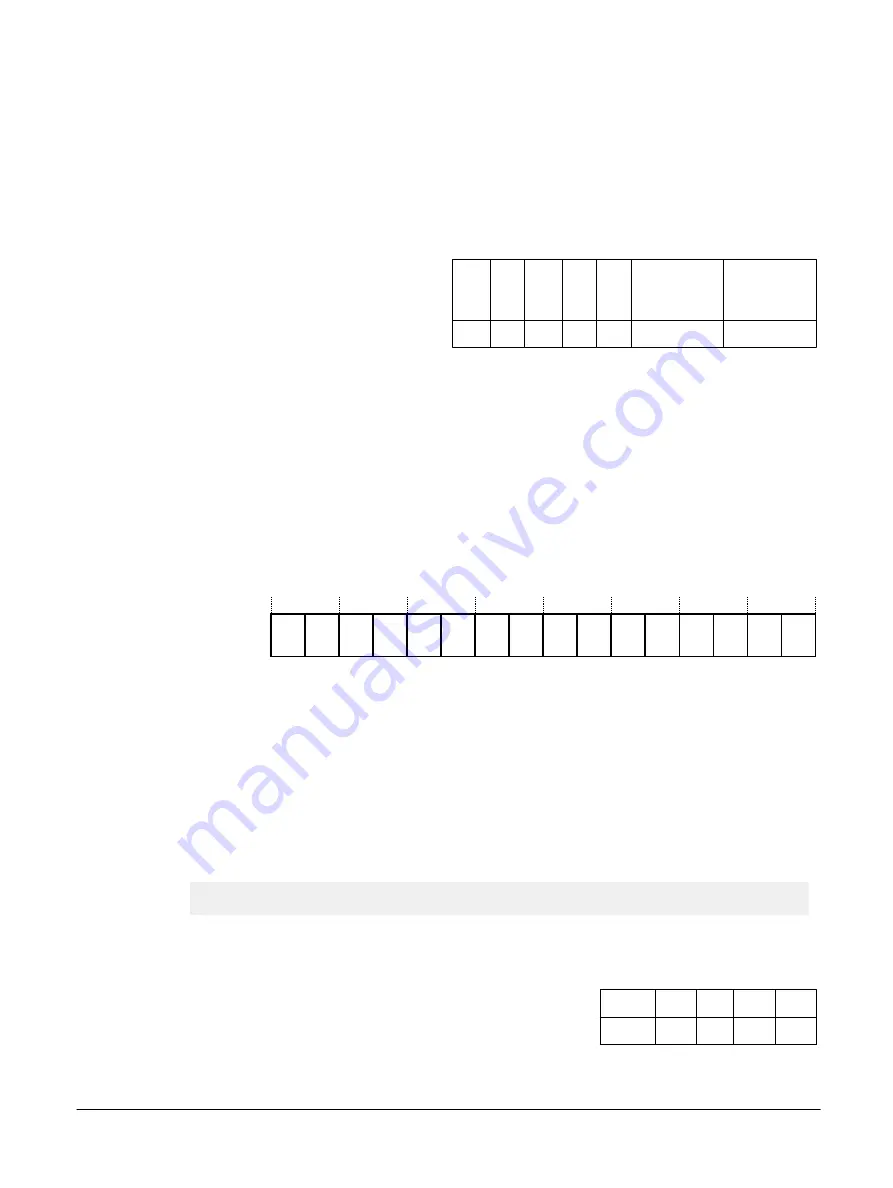

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

D15 D14 D13 D12 D11 D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Figure B1-11 DACR bit assignments

D<n>, bits [2n+1:2n], for n = 0 to 15, [31:0]

Domain

n

access permission, where

n

= 0 to 15. Permitted values are:

0b00

No access. Any access to the domain generates a Domain fault.

0b01

Client. Accesses are checked against the permission bits in the translation tables.

0b11

Manager. Accesses are not checked against the permission bits in the translation tables.

The value

0b10

is reserved.

To access the DACR:

MRC p15, 0, <Rt>, c3, c0, 0 ; Read DACR into Rt

MCR p15, 0, <Rt>, c3, c0, 0 ; Write Rt to DACR

Register access is encoded as follows:

Table B1-41 DACR access encoding

coproc opc1 CRn CRm opc2

1111

000

0011 0000 000

B1 AArch32 system registers

B1.47 Domain Access Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-221

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......