B2.70

IFSR32_EL2 with Short-descriptor translation table format

IFSR32_EL32 has a specific format when using the Short-descriptor translation table format.

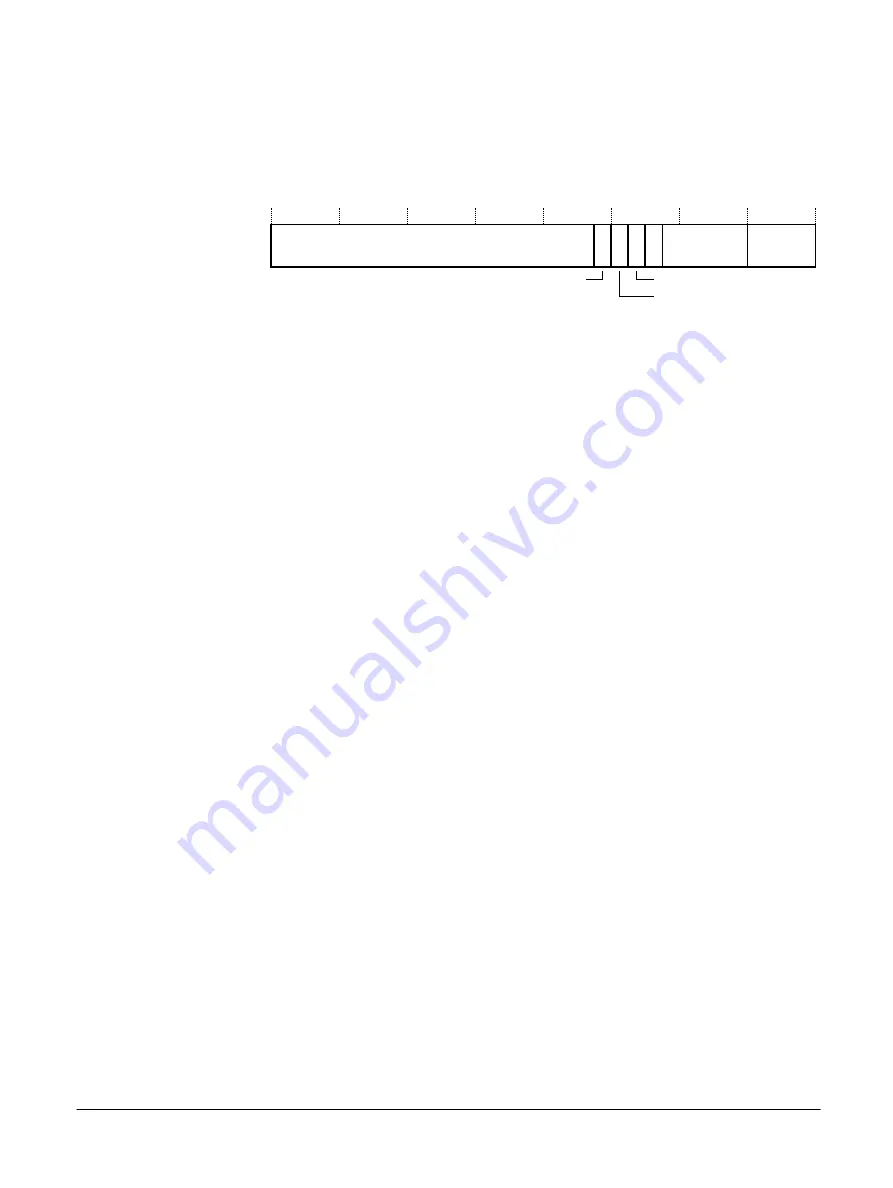

The following figure shows the IFSR32_EL2 bit assignments when using the Short-descriptor translation

table format.

31

13 12 11 10 9 8

4 3

0

RES

0

0

RES

0

FS[3:0]

ExT

FS[4]

RES

0

Figure B2-42 IFSR32_EL2 bit assignments for Short-descriptor translation table format

[31:13]

Reserved,

RES0

.

ExT, [12]

External abort type. This field indicates whether an AXI Decode or Slave error caused an abort:

0

External abort marked as DECERR.

1

External abort marked as SLVERR.

For aborts other than external aborts this bit always returns 0.

[11]

Reserved,

RES0

.

FS[4], [10]

Part of the Fault Status field. See bits [3:0] in this table.

[9]

RAZ.

[8:5]

Reserved,

RES0

.

FS[3:0], [4:0]

Fault Status bits. This field indicates the type of exception generated. Any encoding not listed is

reserved.

0b00010

Debug event.

0b00011

Access flag fault, section.

0b00101

Translation fault, section.

0b00110

Access flag fault, page.

0b00111

Translation fault, page.

0b01000

Synchronous external abort, non-translation.

0b01001

Domain fault, section.

0b01011

Domain fault, page.

0b01100

Synchronous external abort on translation table walk, first level.

0b01101

Permission Fault, Section.

0b01110

Synchronous external abort on translation table walk, second Level.

0b01111

Permission fault, page.

0b10000

TLB conflict abort.

B2 AArch64 system registers

B2.70 IFSR32_EL2 with Short-descriptor translation table format

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-480

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......