1

Trap Non-secure EL0 and EL1 accesses to PMCR_EL0 to EL2.

This bit resets to 0.

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

for more

information.

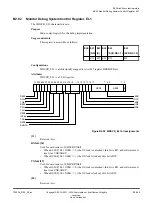

HPMN, [4:0]

Hyp Performance Monitor count. Defines the number of Performance Monitors counters that are

accessible from Non-secure EL1 and EL0 modes.

In Non-secure state, HPMN divides the Performance Monitors counters as follows. For counter

n

in Non-secure state:

For example, If PMnEVCNTR is performance monitor counter

n

then, in Non-secure state:

• If

n

is in the range 0 ≤

n

< HPMN, the counter is accessible from EL1 and EL2, and from

EL0 if permitted by PMUSERENR_EL0. PMCR_EL0.E enables the operation of counters in

this range.

• There are six performance counters, specified by PMCR.N.

If

n

is in the range HPMN ≤

n

< 6, the counter is accessible only from EL2.

MDCR_EL2.HPME enables the operation of counters in this range.

If the field is set to 0, then Non-secure EL0 or EL1 has no access to any counters.

If the field is set to a value greater than six, the behavior is the same as if the value is six.

For reads of MDCR_EL2.HPMN by EL2 or higher, if this field is set to 0 or to a value larger

than PMCR_EL0.N, the processor returns the value that was written to MDCR_EL2.HPMN.

This field resets to

0x6

.

To access the MDCR_EL2:

MRS <Xt>, MDCR_EL2 ; Read MDCR_EL2 into Xt

MSR MDCR_EL2, <Xt> ; Write Xt to MDCR_EL2

Register access is encoded as follows:

Table B2-74 MDCR_EL2 access encoding

op0 op1 CRn CRm op2

11

100 0001 0001 001

B2 AArch64 system registers

B2.80 Monitor Debug Configuration Register, EL2

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-502

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......