A.9

ACP interface signals

The AXI protocol supports clock, configuration, and data handling signals if the processor implements

the ACP slave interface to an external master to make coherent request to the shared L2 cache of the

cluster.

This interface exists only if the processor is configured to have the ACP interface.

All ACP channels must be balanced with respect to

CLKIN

and timed relative to

ACLKENS

.

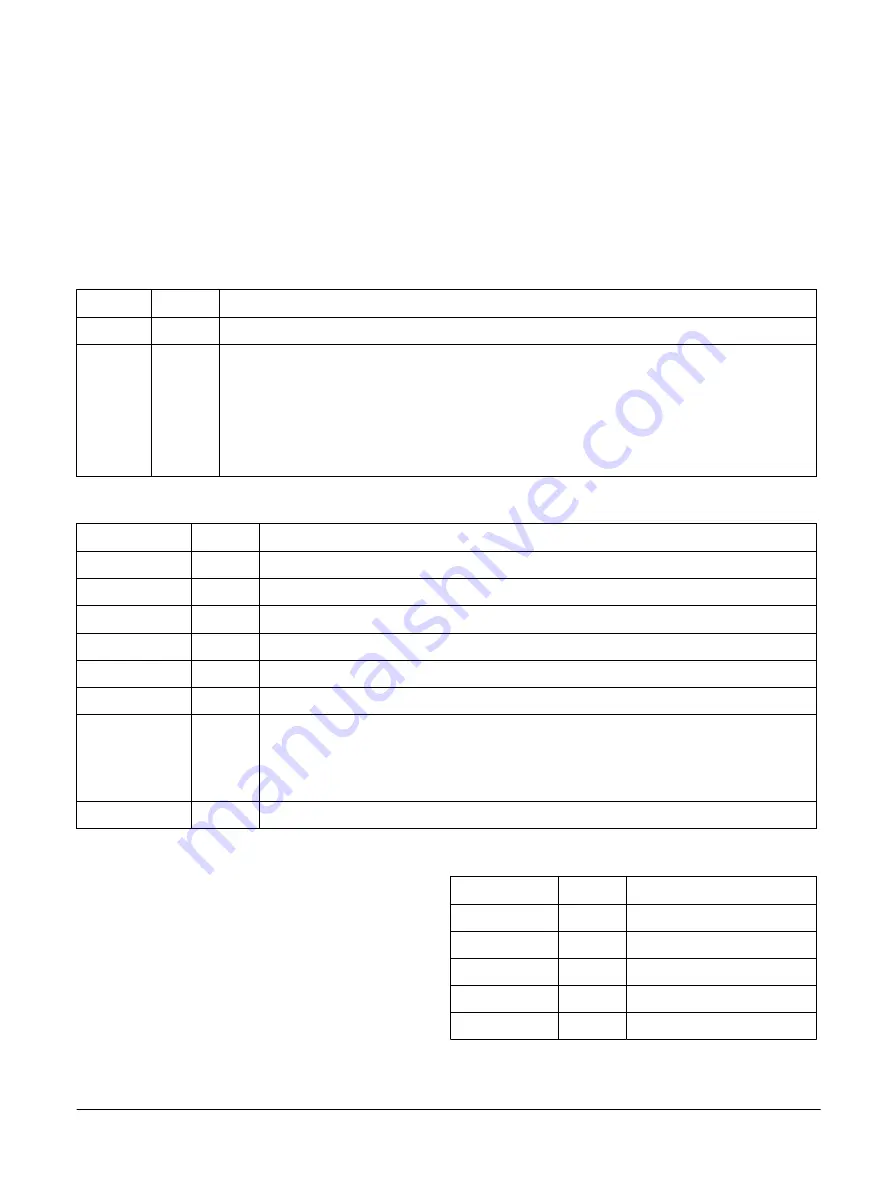

Table A-11 ACP clock and Configuration signals

Signal

Direction Description

ACLKENS

Input

AXI slave bus clock enable.

AINACTS

Input

ACP master is inactive and is not participating in coherency. There must be no outstanding transactions

when the master asserts this signal, and while it is asserted the master must not send any new transactions:

0

ACP Master is active.

1

ACP Master is inactive.

This signal must be asserted before the processor enters the low-power L2 WFI state.

Table A-12 ACP write address channel signals

Signal

Direction Description

AWREADYS

Output

Write address ready

AWVALIDS

Input

Write address valid

AWIDS[4:0]

Input

Write address ID

AWADDRS[39:0]

Input

Write address

AWLENS[7:0]

Input

Write burst length

AWCACHES[3:0]

Input

Write cache type

AWUSERS[1:0]

Input

Write attributes:

[0]

Inner Shareable.

[1]

Outer Shareable.

AWPROTS[2:0]

Input

Write protection type

Table A-13 ACP write data channel signals

Signal

Direction Description

WREADYS

Output

Write data ready

WVALIDS

Input

Write data valid

WDATAS[127:0]

Input

Write data

WSTRBS[15:0]

Input

Write byte-lane strobes

WLASTS

Input

Write data last transfer indication

A Signal Descriptions

A.9 ACP interface signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-A-859

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......