B.4

Armv8 Debug UNPREDICTABLE behaviors

This section describes the behavior that the Cortex

‑

A35 processor implements when:

• A topic has multiple options.

• The behavior differs from either or both of the Options and Preferences behaviors.

Note

This section does not describe the behavior when a topic only has a single option and the processor

implements the preferred behavior.

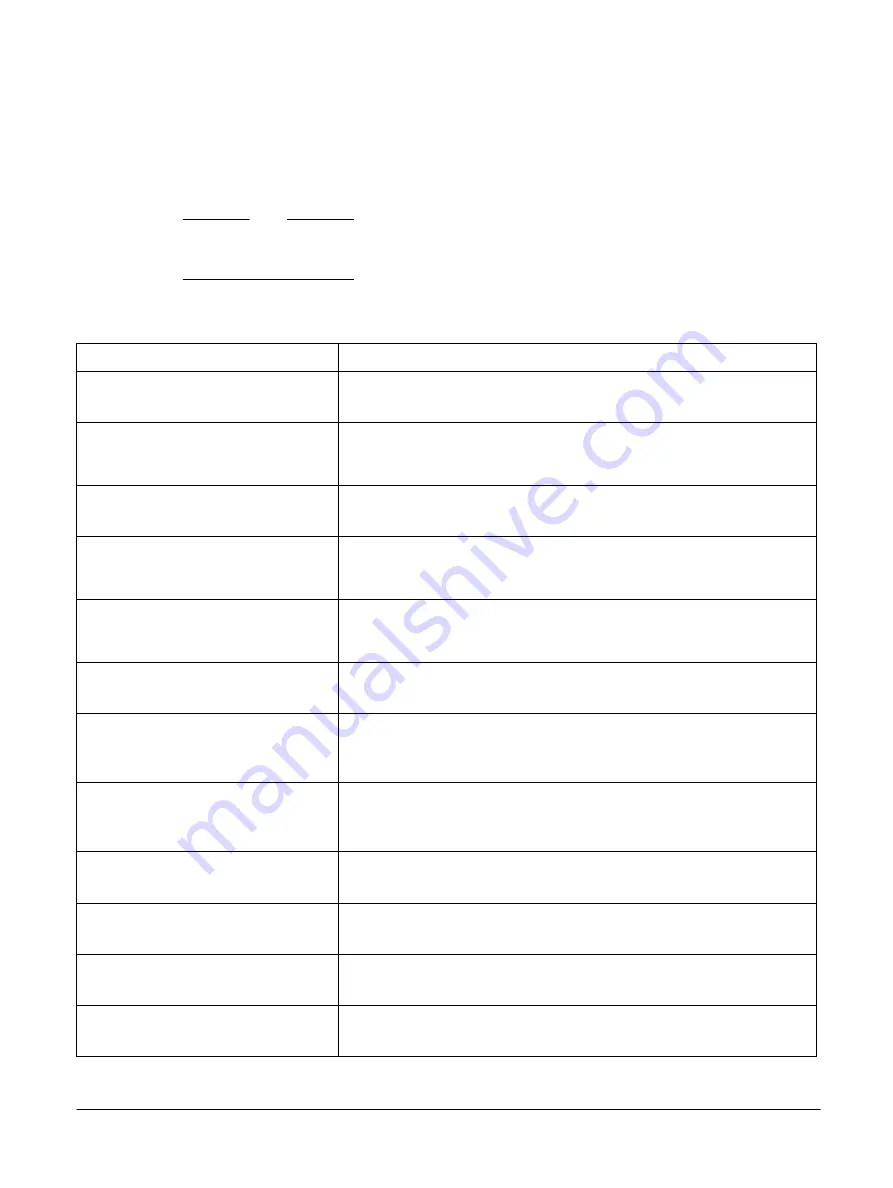

Table B-1 Armv8 Debug UNPREDICTABLE behaviors

Scenario

Behavior

A32 BKPT instruction with condition code

not AL

The processor implements the following preferred option:

•

Executed unconditionally.

Address match breakpoint match only on

second halfword of an instruction

The processor generates a breakpoint on the instruction, unless it is a breakpoint on

the second half of the first 32-bit instruction. In this case the breakpoint is taken on the

following instruction.

Address matching breakpoint on A32

instruction with DBGBCRn.BAS=1100

The processor implements the following option:

•

Does match.

Address match breakpoint match on T32

instruction at 2 with

DBGBCRn.BAS=1111

The processor implements the following option:

•

Does match.

Address mismatch breakpoint match on T32

instruction at D2 with

DBGBCRn.BAS=1111

The processor implements the following option:

•

Does match.

Other mismatch breakpoint matches any

address in current mode and state

The processor implements the following option:

•

Immediate breakpoint debug event.

Mismatch breakpoint on branch to self

The processor implements the following option:

•

Instruction is stepped an

UNKNOWN

number of times, while it continues to branch

to itself.

Link to non-existent breakpoint or breakpoint

that is not context-aware

The processor implements the following option:

•

No Breakpoint or Watchpoint debug event is generated, and the LBN field of the

linker

reads

UNKNOWN

.

DBGWCRn_EL1.MASK!=00000 and

DBGWCRn_EL1.BAS!=11111111

The processor behaves as indicated in the sole Preference:

•

DBGWCRn_EL1.BAS is ignored and treated as if

0x11111111

.

Address-matching Vector catch on 32-bit T32

instruction at (vector-2)

The processor implements the following option:

•

Does match.

Address-matching Vector catch on 32-bit T32

instruction at (2)

The processor implements the following option:

•

Does match.

Address-matching Vector catch and

Breakpoint on same instruction

The processor implements the following option:

•

Report Breakpoint.

B AArch32 UNPREDICTABLE Behaviors

B.4 Armv8 Debug UNPREDICTABLE behaviors

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-B-885

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......