B1.87

Instruction Fault Status Register

The IFSR characteristics are:

Purpose

Holds status information about the last instruction fault.

Usage constraints

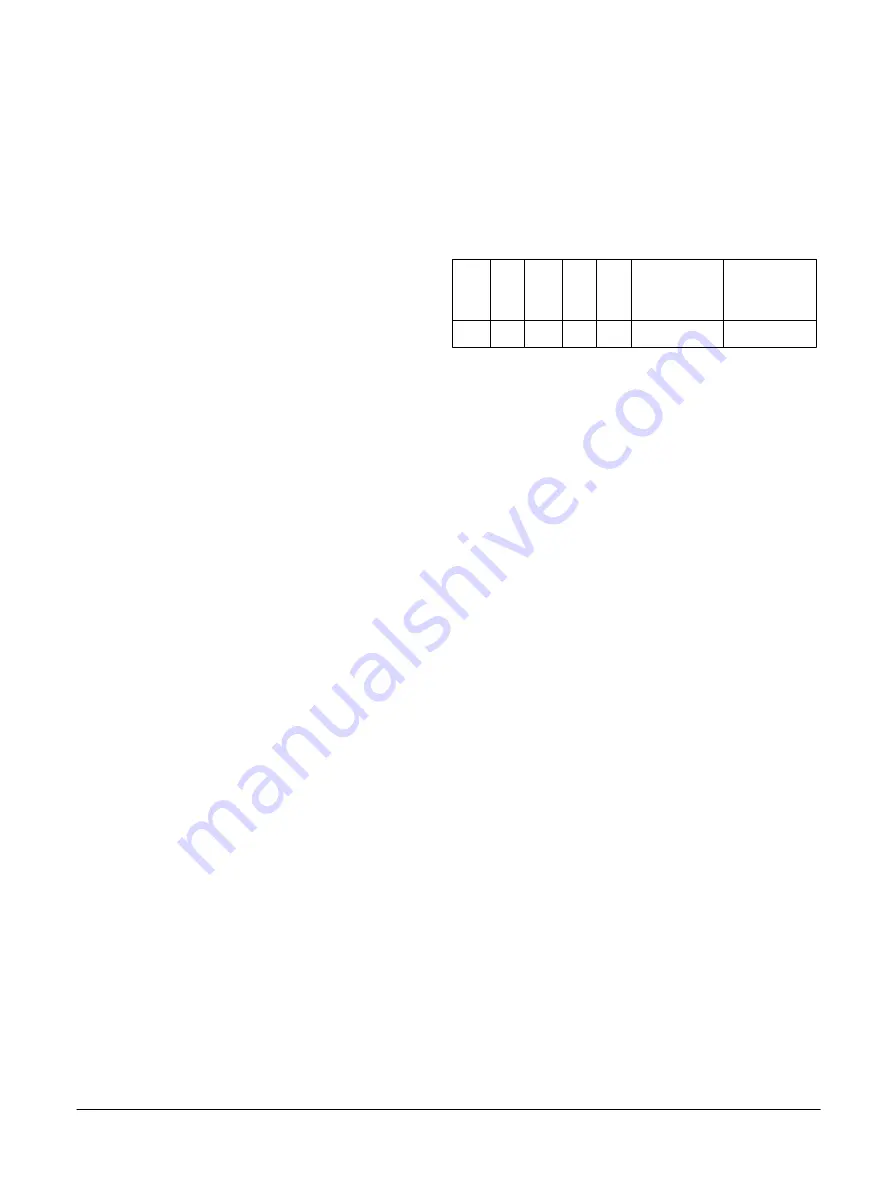

This register is accessible as follows:

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW RW RW

RW

Configurations

IFSR (NS) is architecturally mapped to AArch64 register IFSR32_EL2. See

.

If EL3 is using AArch32, there are separate Secure and Non-secure instances of this register.

Attributes

IFSR is a 32-bit register.

There are two formats for this register. The current translation table format determines which format of

the register is used.

B1 AArch32 system registers

B1.87 Instruction Fault Status Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-294

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......