B1.98

Non-Secure Access Control Register

The NSACR characteristics are:

Purpose

Defines the Non-secure access permission to CP0 to CP13.

Usage constraints

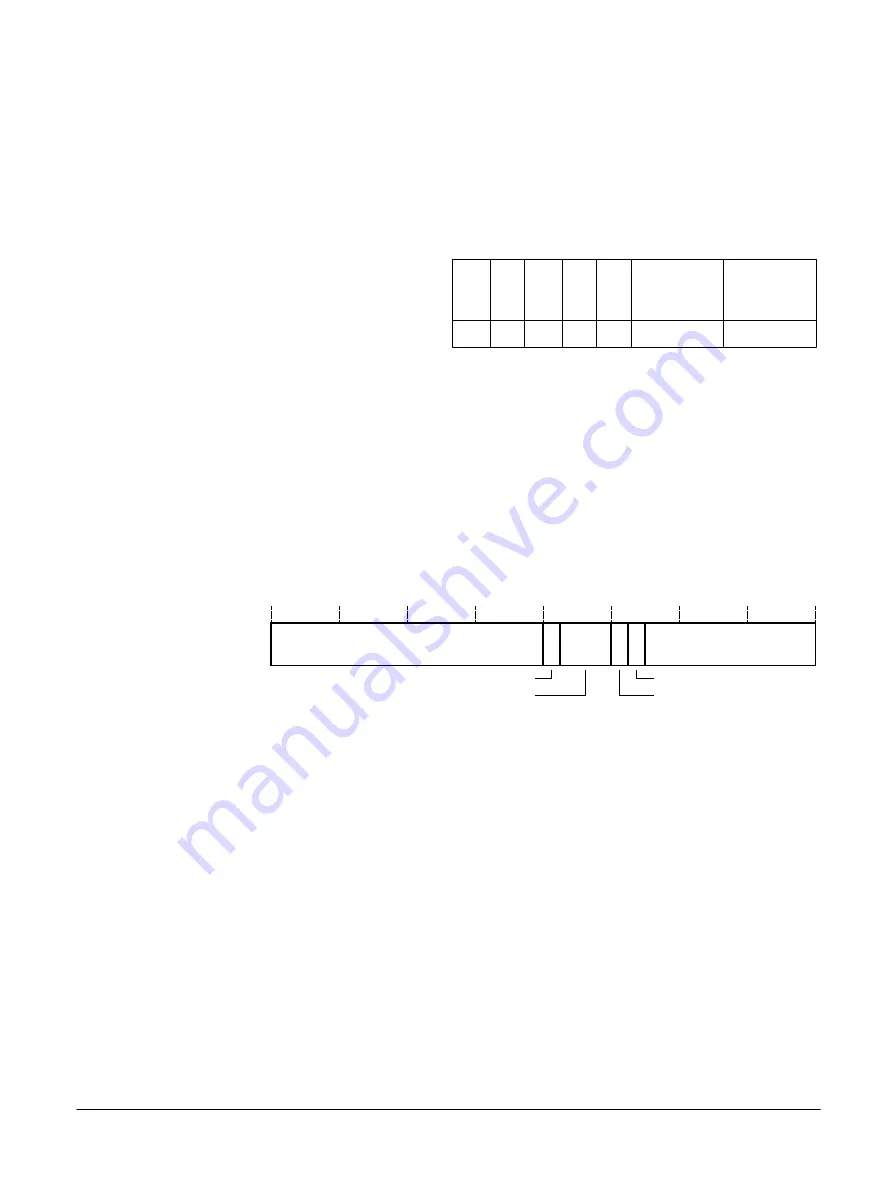

This register is accessible as follows:

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RO

RO

RO

RW

RW

Any read or write to NSACR in Secure EL1 state in AArch32 is trapped as an exception to EL3.

Configurations

There is one copy of this register that is used in both Secure and Non-secure states.

If EL3 is using AArch64, then any reads of the NSACR from Non-secure EL2 or Non-secure

EL1 using AArch32 return a fixed value of

0x00000C00

.

In AArch64, the NSACR functionality is replaced by the behavior in CPTR_EL3.

If EL3 is using AArch32, write access to NSACR is disabled when the

CP15SDISABLE2

signal is asserted HIGH.

Attributes

NSACR is a 32-bit register.

31

16 15 14

12 11 10 9

0

RES

0

RES

0

NSASEDIS

Reserved

cp10

cp11

RES

0

Figure B1-52 NSACR bit assignments

[31:16]

Reserved,

RES0

.

NSASEDIS, [15]

Disable Non-secure Advanced SIMD functionality:

0

This bit has no effect on the ability to write CPACR.ASEDIS, this is the reset value.

1

When executing in Non-secure state, the CPACR.ASEDIS bit has a fixed value of 1 and

writes to it are ignored.

If Advanced SIMD and floating-point are not implemented, this bit is

RES0

.

[14:12]

Reserved,

RES0

.

cp11, [11]

Non-secure access to CP11 enable:

B1 AArch32 system registers

B1.98 Non-Secure Access Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-317

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......