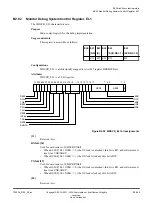

[28:3]

Reserved,

RES0

.

L2 dynamic retention control, [2:0]

L2 dynamic retention control. The possible values are:

0b000

L2 dynamic retention disabled. This is the reset value.

0b001

2 Generic Timer ticks required before retention entry.

0b010

8 Generic Timer ticks required before retention entry.

0b011

32 Generic Timer ticks required before retention entry.

0b100

64 Generic Timer ticks required before retention entry.

0b101

128 Generic Timer ticks required before retention entry.

0b110

256 Generic Timer ticks required before retention entry.

0b111

512 Generic Timer ticks required before retention entry.

To access the L2ECTLR_EL1:

MRS Rt, S3_1_C11_C0_3; Read L2ECTLR_EL1 into Rt

MSR S3_1_C11_C0_3, Rt; Write Rt to L2ECTLR_EL1

Register access is encoded as follows:

Table B2-66 L2ECTLR_EL1 access encoding

op0 op1 CRn CRm op2

11

001 1011 0000 011

B2 AArch64 system registers

B2.75 L2 Extended Control Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-492

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......