B1.4

c2 registers

The processor can access different 32-bit wide system registers. Registers where CRn has the value two

are called c2 registers.

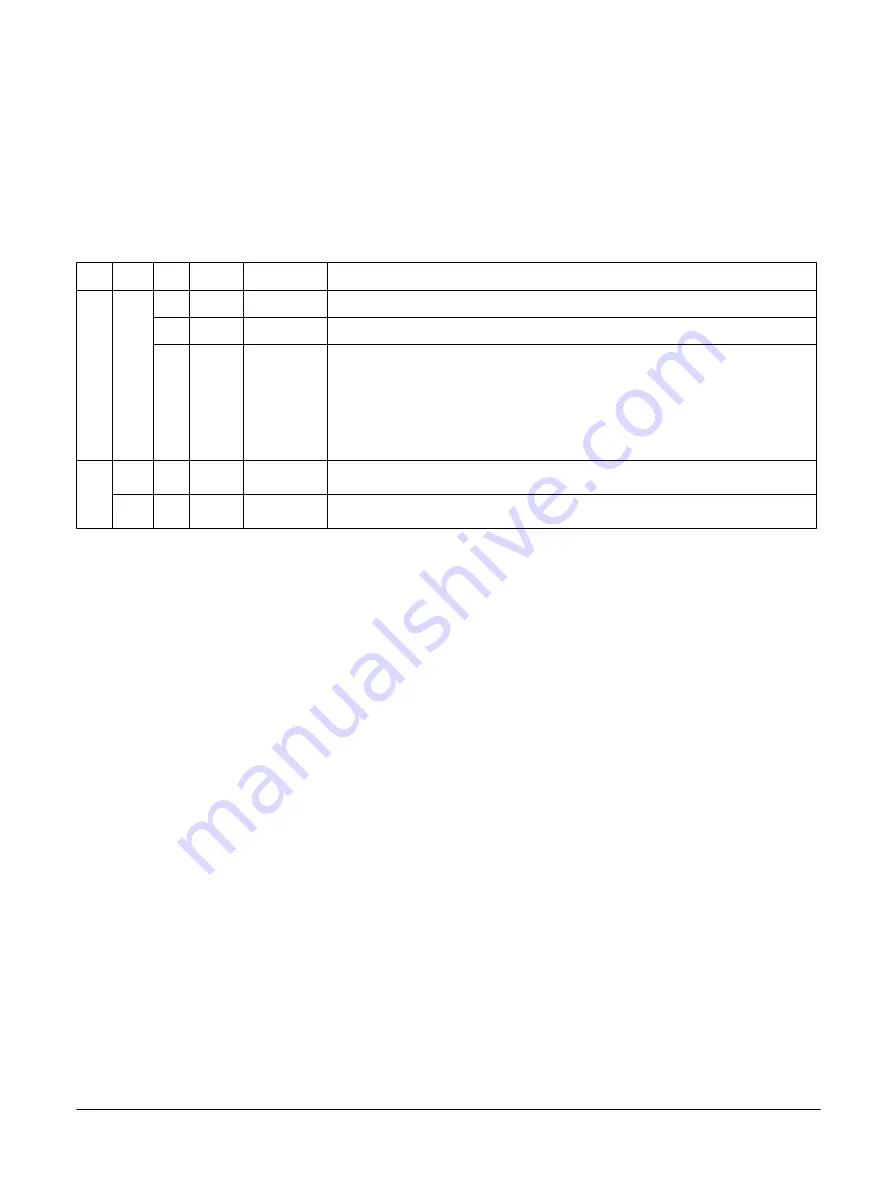

The following table shows the 32-bit wide system registers you can access when the processor is in

AArch32 state and the value of CRn is c2.

Table B1-4 c2 register summary

Op1 CRm Op2 Name

Reset

Description

0

c0

0

TTBR0 UNK

B1.113 Translation Table Base Register 0

1

TTBR1 UNK

B1.116 Translation Table Base Register 1

2

TTBCR

0x00000000

B1.110 Translation Table Base Control Register

The reset value is

0x00000000

for the Secure copy of the register. The reset value for

the EAE bit of the Non-secure copy of the register is

0x0

. You must program the Non-

secure copy of the register with the required initial value, as part of the processor boot

sequence.

4

c0

2

HTCR

UNK

B1.70 Hyp Translation Control Register

c1

2

VTCR

UNK

B1.122 Virtualization Translation Control Register

B1 AArch32 system registers

B1.4 c2 registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-156

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......