When this register has an architecturally-defined reset value, this field resets to a value that is

architecturally UNKNOWN on Warm reset.

TDCC, [12]

Traps EL0 accesses to the DCC registers to EL1, from both Execution states:

0

EL0 using AArch64:

• EL0 accesses to the MDCCSR_EL0, DBGDTR_EL0, DBGDTRTX_EL0, and

DBGDTRRX_EL0 registers are not trapped to EL1.

EL0 using AArch32:

• EL0 accesses to the DBGDSCRint, DBGDTRRXint, DBGDTRTXint, DBGDIDR,

DBGDSAR, and DBGDRAR registers are not trapped to EL1.

1

EL0 using AArch64:

• EL0 accesses to the MDCCSR_EL0, DBGDTR_EL0, DBGDTRTX_EL0, and

DBGDTRRX_EL0 registers are trapped to EL1.

EL0 using AArch32:

• EL0 accesses to the DBGDSCRint, DBGDTRRXint, DBGDTRTXint, DBGDIDR,

DBGDSAR, and DBGDRAR registers are trapped to EL1.

All accesses to these AArch32 registers are trapped, including LDC and STC accesses to

DBGDTRTXint and DBGDTRRXint, and MRRC accesses to DBGDSAR and DBGDRAR.

Traps of AArch32 PL0 accesses to the DBGDTRRXint and DBGDTRTXint are ignored in

Debug state.

When this register has an architecturally-defined reset value, this field resets to a value that is

architecturally UNKNOWN on Warm reset.

[11:7]

Reserved,

RES0

.

ERR, [6]

Used for save/restore of EDSCR.ERR.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

[5:1]

Reserved,

RES0

.

SS, [0]

Software step control bit. If EL

D

is using AArch64, enable Software step. Permitted values are:

0

Software step is disabled.

1

Software step is unabled.

RES0

if EL

D

is using AArch32.

When this register has an architecturally-defined reset value, this field resets to a value that is

architecturally UNKNOWN on Warm reset.

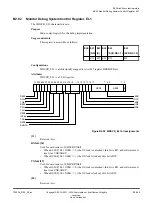

To access the MDSCR_EL1:

MRS <Xt>, MDSCR_EL1 ; Read MDSCR_EL1 into Xt

MSR MDSCR_EL1, <Xt> ; Write Xt to MDSCR_EL1

Register access is encoded as follows:

B2 AArch64 system registers

B2.82 Monitor Debug System Control Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-508

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......