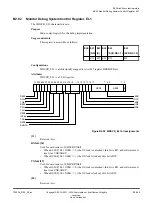

Valid, [31]

Valid bit. This bit is set to 1 on the first memory error. It is a sticky bit so that after it is set, it

remains set until the register is written.

The reset value is 0.

RAMID, [30:24]

RAM Identifier. Indicates the RAM in which the first memory error occurred. The possible

values are:

0x10

L2 tag RAM.

0x11

L2 data RAM.

0x12

SCU snoop filter RAM.

[23:22]

Reserved,

RES0

.

CPUID/Way, [21:18]

Indicates the RAM where the first memory error occurred.

L2 tag RAM

0x0

Way 0

0x1

Way 1

...

0x6

Way 6

0x7

Way 7

L2 data RAM

0x0

Bank 0

0x1

Bank 1

...

0x7

Bank 7

0x8

-

0x

F

Unused

SCU snoop filter RAM

0x0

CPU0:Way0

0x1

CPU0:Way1

...

0xE

CPU3:Way2

0xF

CPU3:Way3

[17]

Reserved,

RES0

.

RAM address, [16:3]

Indicates the index address of the first memory error.

[2:0]

Reserved,

RES0

.

• A fatal error results in the RAMID, CPU ID/Way and RAM address recording the fatal error, even if

the sticky bit was set.

• If two or more memory errors in the same RAM occur in the same cycle, only one error is reported.

B2 AArch64 system registers

B2.76 L2 Memory Error Syndrome Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-494

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......