A3.3

Resets

The Cortex

‑

A35 processor has active-LOW reset input signals that can be asynchronously asserted

HIGH to LOW, or deasserted LOW to HIGH.

nCPUPORESET[CN:0]

Where

CN

is the number of cores minus one.

Power On reset signals. These primary, cold reset signals initialize all resettable registers in the

corresponding core, including debug registers and ETM registers.

nCORERESET[CN:0]

These primary reset signals initialize all resettable registers in the corresponding core, not

including debug registers and ETM registers.

nPRESETDBG

This single, processor-wide signal resets the integrated CoreSight components that connect to

the external

PCLK

domain, such as debug logic.

nL2RESET

This single, processor-wide signal resets all resettable registers in the L2 memory system and

the logic in the SCU or mini-SCU.

nMBISTRESET

An external MBIST controller can use this signal to reset the entire SoC. The

nMBISTRESET

signal resets all resettable registers in the cluster, for entry into, and exit from, MBIST mode.

Reset synchronization logic inside the processor ensures that reset deassertion is synchronous for all

resettable registers. The processor clock is not required for reset assertion, but it must be present for reset

deassertion to ensure reset synchronization.

In general, the reset time only requires three processor clock cycles.

Note

The application of a retention state can affect how long reset assertion is required. You must hold the

reset signal active-LOW until the power returns and the unit or processor is ready for the reset to take

effect if:

• The Advanced SIMD and floating-point unit of a core undergoing a reset is in retention state.

• A core that is being reset is in retention state.

The time that is taken for retention exit and the behavior of the power controller varies by partner and by

implementation.

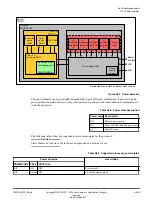

The following table describes the valid reset signal combinations. All other combinations of reset signals

are illegal. In the table, n designates the core that is reset.

A3 Clocks, Resets, and Input Synchronization

A3.3 Resets

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A3-52

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......