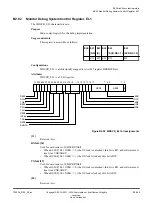

[29:25]

Reserved,

RES0

.

MT, [24]

Indicates whether the lowest level of affinity consists of logical cores that are implemented

using a multi-threading type approach. This value is:

0

Performance of cores at the lowest affinity level is largely independent.

Aff2, [23:16]

Affinity level 2. Second highest level affinity field.

Indicates the value read in the

CLUSTERIDAFF2

configuration signal.

Aff1, [15:8]

Affinity level 1. Third highest level affinity field.

Indicates the value read in the

CLUSTERIDAFF1

configuration signal.

Aff0, [7:0]

Affinity level 0. Lowest level affinity field.

Indicates the core number in the Cortex

‑

A35 processor. The possible values are:

0x0

A cluster with one core only.

0x0

,

0x1

A cluster with two cores.

0x0

,

0x1

,

0x2

A cluster with three cores.

0x0

,

0x1

,

0x2

,

0x3

A cluster with four cores.

To access the MPIDR_EL1:

MRS <Xt>, MPIDR_EL1 ; Read MPIDR_EL1 into Xt

Register access is encoded as follows:

Table B2-78 MPIDR_EL1 access encoding

op0 op1 CRn CRm op2

11

000 0000 0000 101

The EDDEVAFF0 and EDDEVAFF1 can be accessed through the external debug interface, offsets

0xFA8

and

0xFAC

respectively.

B2 AArch64 system registers

B2.84 Multiprocessor Affinity Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-513

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......