C9.4

ROM entry registers

The characteristics of the ROMENTRY

n

are:

Purpose

Indicates to a debugger whether the debug component is present in the debug logic of the

processor. There are 16 ROMENTRY registers in the Cortex

‑

A35 processor.

Usage constraints

These registers are accessible as follows:

Off DLK OSLK EDAD SLK Default

-

-

-

-

-

RO

C1.4 External access permissions to debug registers

codes.

Configurations

Attributes

See

C9.3 ROM table register summary

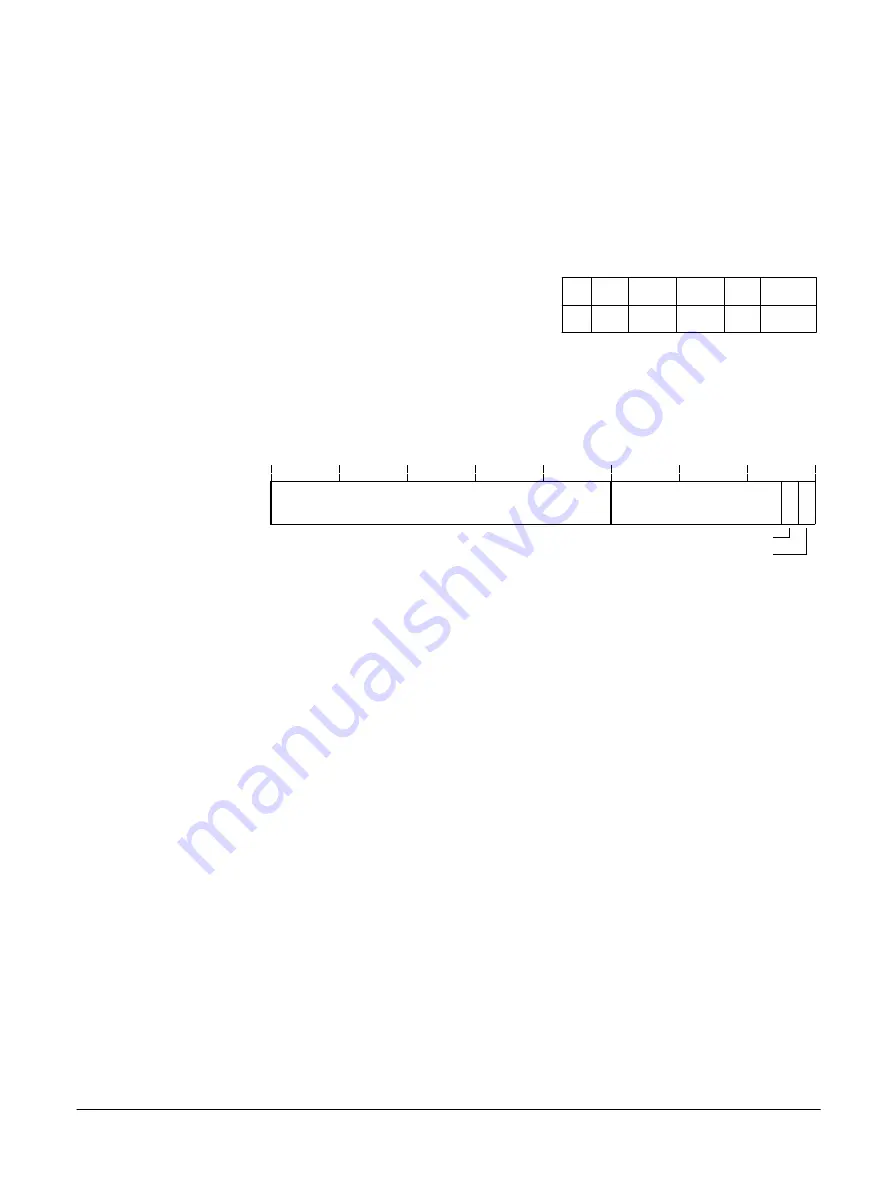

31

0

RES

0

Format

1

2

11

Component present

Address offset

12

Figure C9-1 ROMENTRY bit assignments

Address offset, [31:12]There is one copy of this register that is used in both Secure and Non-secure

states.

Address offset for the debug component.

There is one copy of this register that is used in both Secure andNegative values of address

offsets are permitted using the two’s complement of the offset.

[11:2]

Reserved,

RES0

.

Format, [1]

Format of the ROM table entry. The value for all ROMENTRY registers is:

0

End marker.

1

32-bit format.

Component present, [0]

Indicates whether the component is present:

0

Component is not present.

1

Component is present.

The debug, CTI, and PMU components for core 0 are always present.

The Physical Address of a debug component is determined by shifting the address offset 12 places to the

left and adding the result to the Physical Address of the Cortex

‑

A35 processor ROM table.

C9 ROM table

C9.4 ROM entry registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C9-673

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......