A4.5

L2 Wait for Interrupt

When all the cores are in WFI low-power state, the shared L2 memory system logic that is common to all

the cores can also enter a WFI low-power state.

Entry into L2 WFI low-power state can occur only if specific requirements are met and the following

sequence applied:

• All cores are in WFI low-power state and therefore, the

STANDBYWFI

output for each core is

asserted. Assertion of all the cores

STANDBYWFI

outputs guarantees that all the cores are in idle

and low-power state. All clocks in the cores, with the exception of a small amount of clock wakeup

logic, are disabled.

• If configured with ACE, the SoC asserts the input pin

ACINACTM

to idle the AXI master interface.

It indicates that no snoop requests will be made from the external memory system.

• If configured with a CHI interface, the SoC asserts the input pin

SINACT

to idle the CHI master

interface. It indicates that no snoop requests will be made from the external memory system.

• If configured with an ACP interface, the SoC asserts the

AINACTS

input pin to idle the ACP

interface. It indicates that the SoC sends no more transactions on the ACP interface.

When the L2 memory system completes the outstanding transactions for AXI, ACE, or CHI interfaces, it

can then enter the L2 WFI low-power state. On entry into L2 WFI low-power state,

STANDBYWFIL2

is asserted. Assertion of

STANDBYWFIL2

guarantees that the L2 memory system is idle and does not

accept new transactions.

Exit from L2 WFI low-power state occurs on one of the following events:

• A physical IRQ or FIQ interrupt.

• A debug event.

• Powerup or warm reset.

When a core exits permanently from WFI low-power state,

STANDBYWFI

for that core is deasserted.

When the L2 memory system logic exits from WFI low-power state,

STANDBYWFIL2

is deasserted.

The SoC must continue to assert

ACINACTM

or

SINACT

until

STANDBYWFIL2

has deasserted.

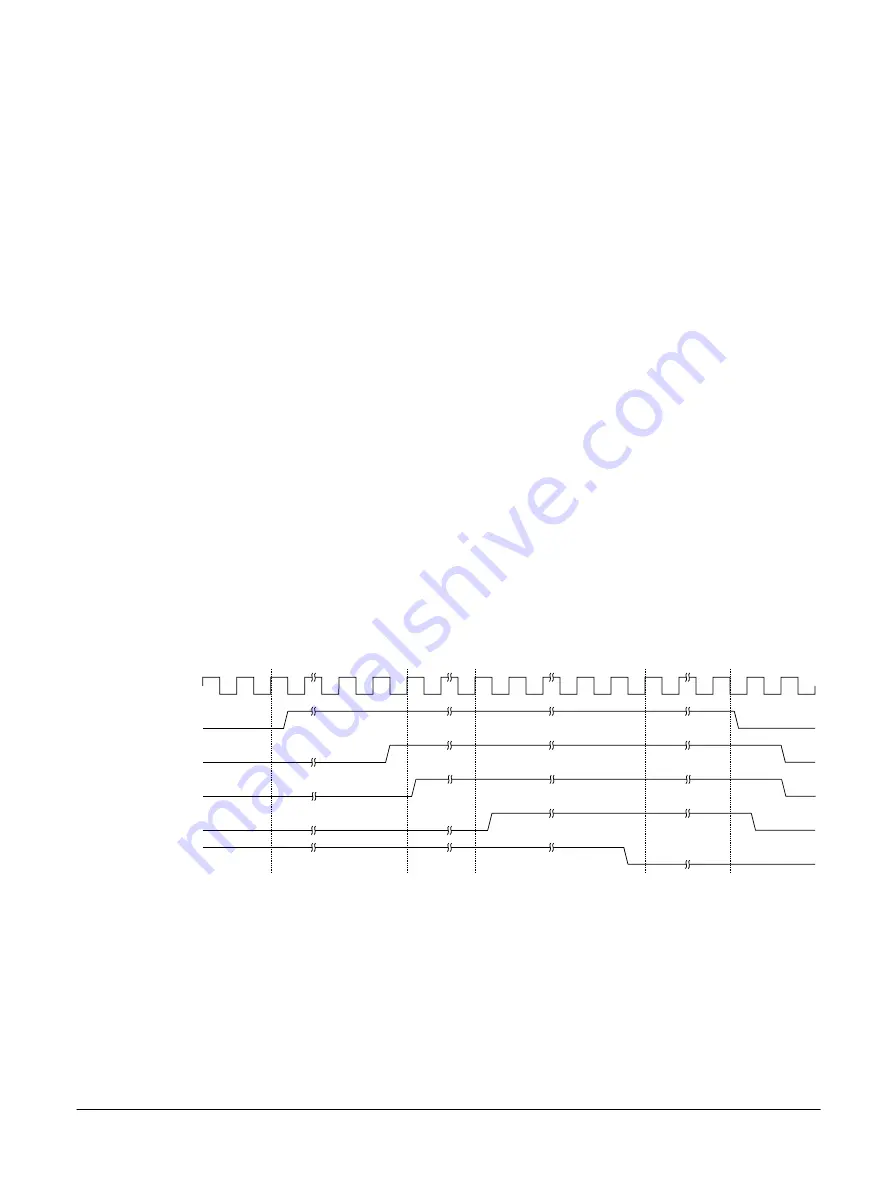

The following figure shows the L2 WFI timing for a 4-core configuration.

CLKIN

STANDBYWFI[3:0]

ACINACTM

STANDBYWFIL2

nIRQ

AINACTS

Figure A4-3 L2 Wait For Interrupt timing

A4 Power Management

A4.5 L2 Wait for Interrupt

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A4-64

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......