C11.6

Auxiliary Control Register

The TRCAUXCTLR characteristics are:

Purpose

The function of this register is to provide

IMPLEMENTATION DEFINED

configuration and control

options.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

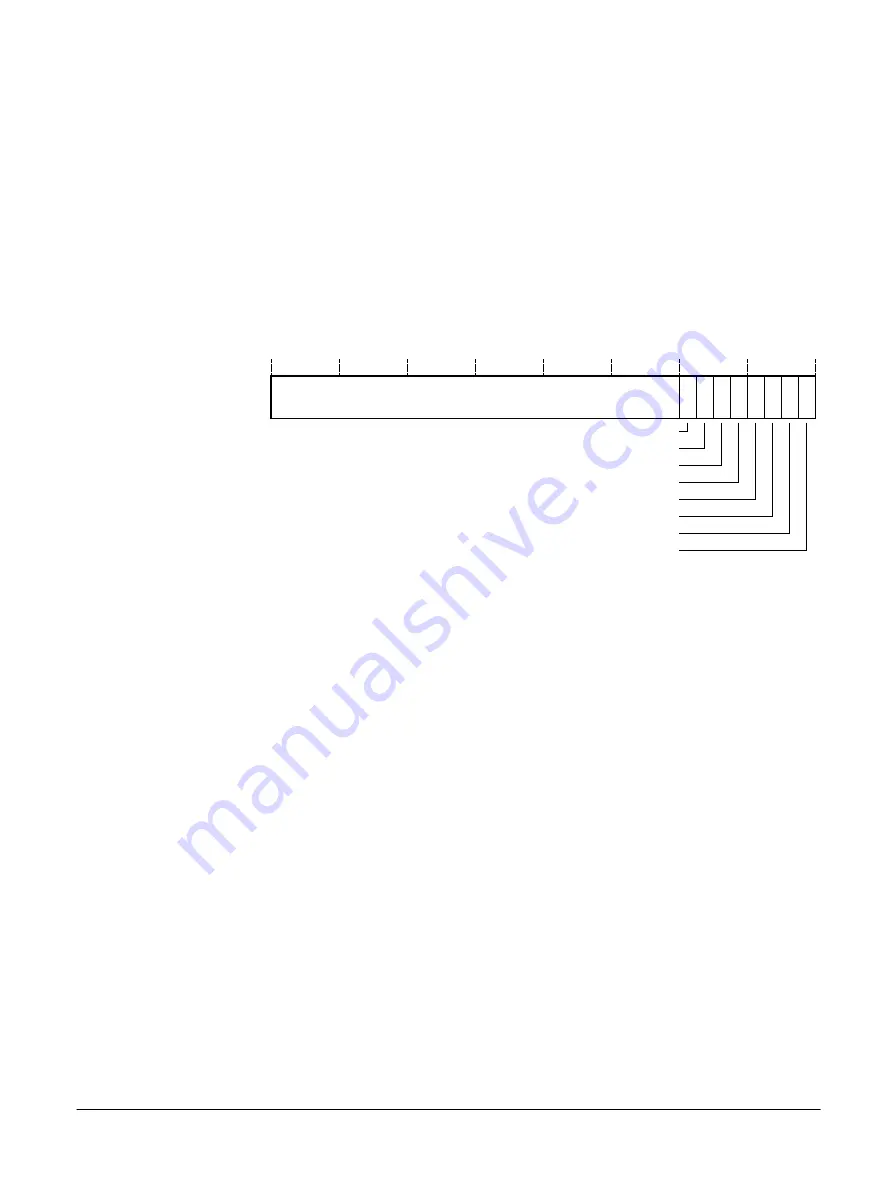

See

31

0

RES

0

8 7

COREIFEN

RES

0

AUTHNOFLUSH

TSNODELAY

6 5 4 3 2 1

SYNCDELAY

OVFLW

IDLEACK

AFREADY

Figure C11-5 TRCAUXCTLR bit assignments

[31:8]

Reserved,

RES0

.

COREIFEN, [7]

Keep core interface enabled regardless of trace enable register state. The possible values are:

0

Core interface enabled is set by trace enable register state.

1

Enable core interface, regardless of trace enable register state.

[6]

Reserved,

RES0

.

AUTHNOFLUSH, [5]

Do not flush trace on de-assertion of authentication inputs. The possible values are:

0

ETM trace unit FIFO is flushed and ETM trace unit enters idle state when

DBGEN

or

NIDEN

is LOW.

1

ETM trace unit FIFO is not flushed and ETM trace unit does not enter idle state when

DBGEN

or

NIDEN

is LOW.

When this bit is set to 1, the trace unit behavior deviates from architecturally-specified behavior.

TSNODELAY, [4]

Do not delay timestamp insertion based on FIFO depth. The possible values are:

0

Timestamp packets are inserted into FIFO only when trace activity is LOW.

1

Timestamp packets are inserted into FIFO irrespective of trace activity.

SYNCDELAY, [3]

C11 ETM registers

C11.6 Auxiliary Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-741

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......