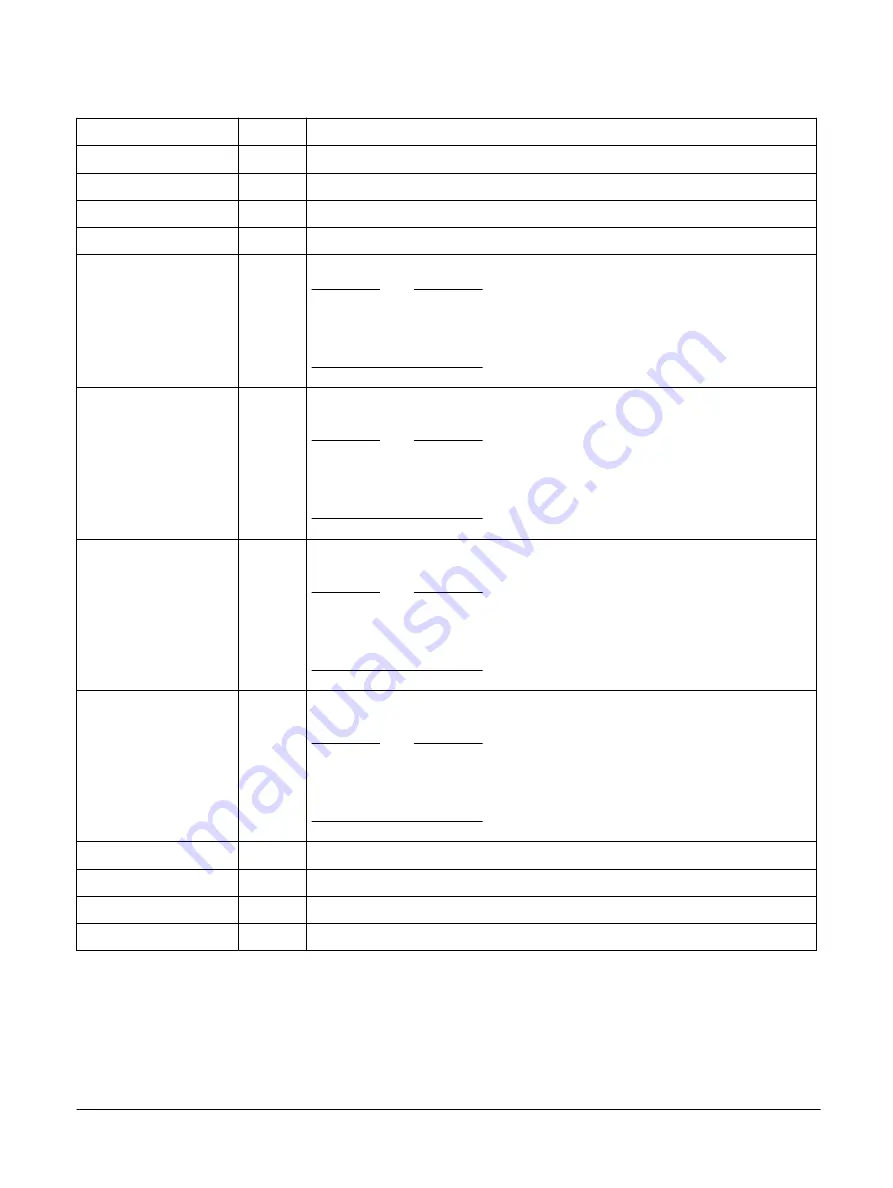

Table A-9 Retention power management signals

Signal

Direction Description

CPUQACTIVE[CN:0]

Output

Indicates whether the referenced core is active

CPUQREQn[CN:0]

Input

Indicates that the power controller is ready to enter or exit retention for the referenced core

CPUQDENY[CN:0]

Output

Indicates that the referenced core denies the power controller retention request

CPUQACCEPTn[CN:0]

Output

Indicates that the referenced core accepts the power controller retention request

NEONQACTIVE[CN:0]

Output

Indicates whether the referenced Advanced SIMD and Floating-point block is active

Note

If a subset of cores in the processor is configured with Advanced SIMD and floating-point

functionality, then

NEONQACTIVE[CN:0]

is replaced with separate

NEONxQACTIVE

signals, where x indicates the core that each signal relates to.

NEONQREQn[CN:0]

Input

Indicates that the power controller is ready to enter or exit retention for the referenced

Advanced SIMD and Floating-point block

Note

If a subset of cores in the processor is configured with Advanced SIMD and floating-point

functionality, then

NEONQREQn[CN:0]

is replaced with separate

NEONxQREQn

signals, where x indicates the core that each signal relates to.

NEONQDENY[CN:0]

Output

Indicates that the referenced Advanced SIMD and Floating-point block denies the power

controller retention request

Note

If a subset of cores in the processor is configured with Advanced SIMD and floating-point

functionality, then

NEONQDENY[CN:0]

is replaced with separate

NEONxQDENY

signals, where x indicates the core that each signal relates to.

NEONQACCEPTn[CN:0]

Output

Indicates that the referenced Advanced SIMD and Floating-point block accepts the power

controller retention request

Note

If a subset of cores in the processor is configured with Advanced SIMD and floating-point

functionality, then

NEONQACCEPTn[CN:0]

is replaced with separate

NEONxQACCEPTn

signals, where x indicates the core that each signal relates to.

L2QACTIVE

Output

Indicates whether the L2 data RAMs are active

L2QREQn

Input

Indicates that the power controller is ready to enter or exit retention for the L2 data RAMs

L2QDENY

Output

Indicates that the L2 data RAMs deny the power controller retention request

L2QACCEPTn

Output

Indicates that the L2 data RAMs accept the power controller retention request

Related information

Chapter A4 Power Management

on page A4-57

A Signal Descriptions

A.7 Power management signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-A-857

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......