B2.7

AArch64 TLB maintenance operations

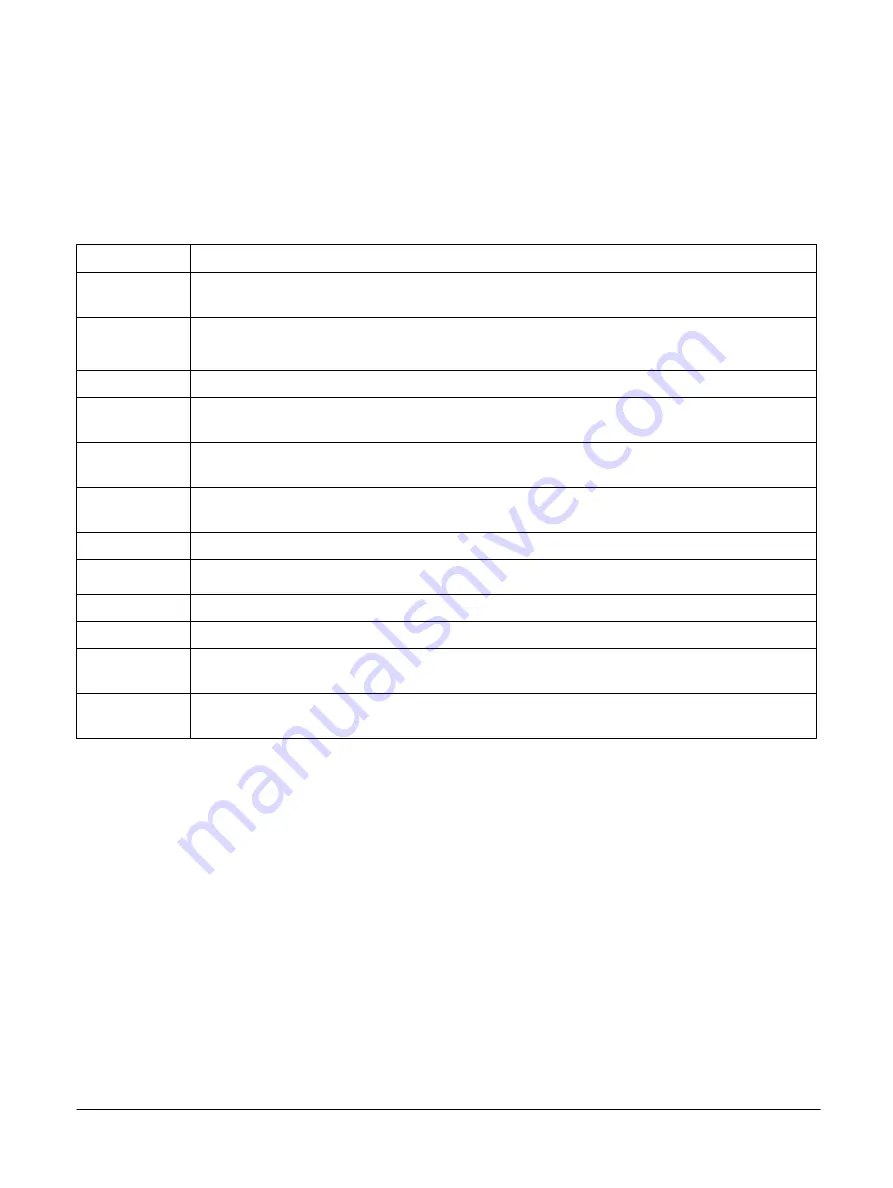

The following table shows the System instructions for TLB maintenance operations in AArch64 state.

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

for more

information about these operations.

Table B2-6 AArch64 TLB maintenance operations

Name

Description

TLBI VMALLE1IS

Invalidate all stage 1 translations used at EL1 with the current

virtual machine identifier

(VMID) in the Inner

Shareable

TLBI VAE1IS

Invalidate translation used at EL1 for the specified VA and

Address Space Identifier

(ASID) and the current

VMID, Inner Shareable

TLBI ASIDE1IS

Invalidate all translations used at EL1 with the current VMID and the supplied ASID, Inner Shareable

TLBI VAAE1IS

Invalidate all translations used at EL1 for the specified address and current VMID and for all ASID values, Inner

Shareable

TLBI VALE1IS

Invalidate all entries from the last level of stage 1 translation table walk used at EL1 with the supplied ASID and

current VMID, Inner Shareable

TLBI VAALE1IS

Invalidate all entries from the last level of stage 1 translation table walk used at EL1 for the specified address and

current VMID and for all ASID values, Inner Shareable

TLBI VMALLE1

Invalidate all stage 1 translations used at EL1 with the current VMID

TLBI VAE1

Invalidate translation used at EL1 for the specified VA and ASID and the current VMID

TLBI ASIDE1

Invalidate all translations used at EL1 with the current VMID and the supplied ASID

TLBI VAAE1

Invalidate all translations used at EL1 for the specified address and current VMID and for all ASID values

TLBI VALE1

Invalidate all entries from the last level of stage 1 translation table walk used at EL1 with the supplied ASID and

current VMID

TLBI VAALE1

Invalidate all entries from the last level of stage 1 translation table walk used at EL1 for the specified address and

current VMID and for all ASID values

The Virtualization registers include additional TLB operations for use in Hyp mode. For more

information, see

B2.14 AArch64 EL2 TLB maintenance operations

.

B2 AArch64 system registers

B2.7 AArch64 TLB maintenance operations

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-370

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......