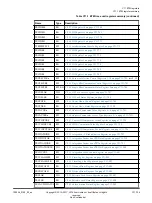

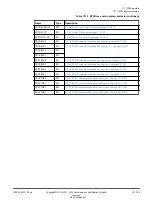

Delay periodic synchronization if FIFO is more than half-full. The possible values are:

0

SYNC packets are inserted into FIFO only when trace activity is low.

1

SYNC packets are inserted into FIFO irrespective of trace activity.

OVFLW, [2]

Force overflow if synchronization is not completed when second synchronization becomes due.

The possible values are:

0

No FIFO overflow when SYNC packets are delayed.

1

Forces FIFO overflow when SYNC packets are delayed.

When this bit is set to 1, the trace unit behavior deviates from architecturally-specified behavior.

IDLEACK, [1]

Force idle-drain acknowledge high, CPU does not wait for trace to drain before entering WFX

state. The possible values are:

0

ETM trace unit idle acknowledge is asserted only when the ETM trace unit is in idle state.

1

ETM trace unit idle acknowledge is asserted irrespective of the ETM trace unit idle state.

When this bit is set to 1, trace unit behavior deviates from architecturally-specified behavior.

AFREADY, [0]

Always respond to AFREADY immediately. Does not have any interaction with FIFO draining,

even in WFI state. The possible values are:

0

ETM trace unit

AFREADYM

output is asserted only when the ETM trace unit is in idle state

or when all the trace bytes in FIFO before a flush request are output.

1

ETM trace unit

AFREADYM

output is always asserted HIGH. When this bit is set to 1,

trace unit behavior deviates from architecturally-specified behavior.

The TRCAUXCTLR can be accessed through the external debug interface, offset

0x018

.

C11 ETM registers

C11.6 Auxiliary Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-742

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......