B2.6

AArch64 Cache maintenance operations

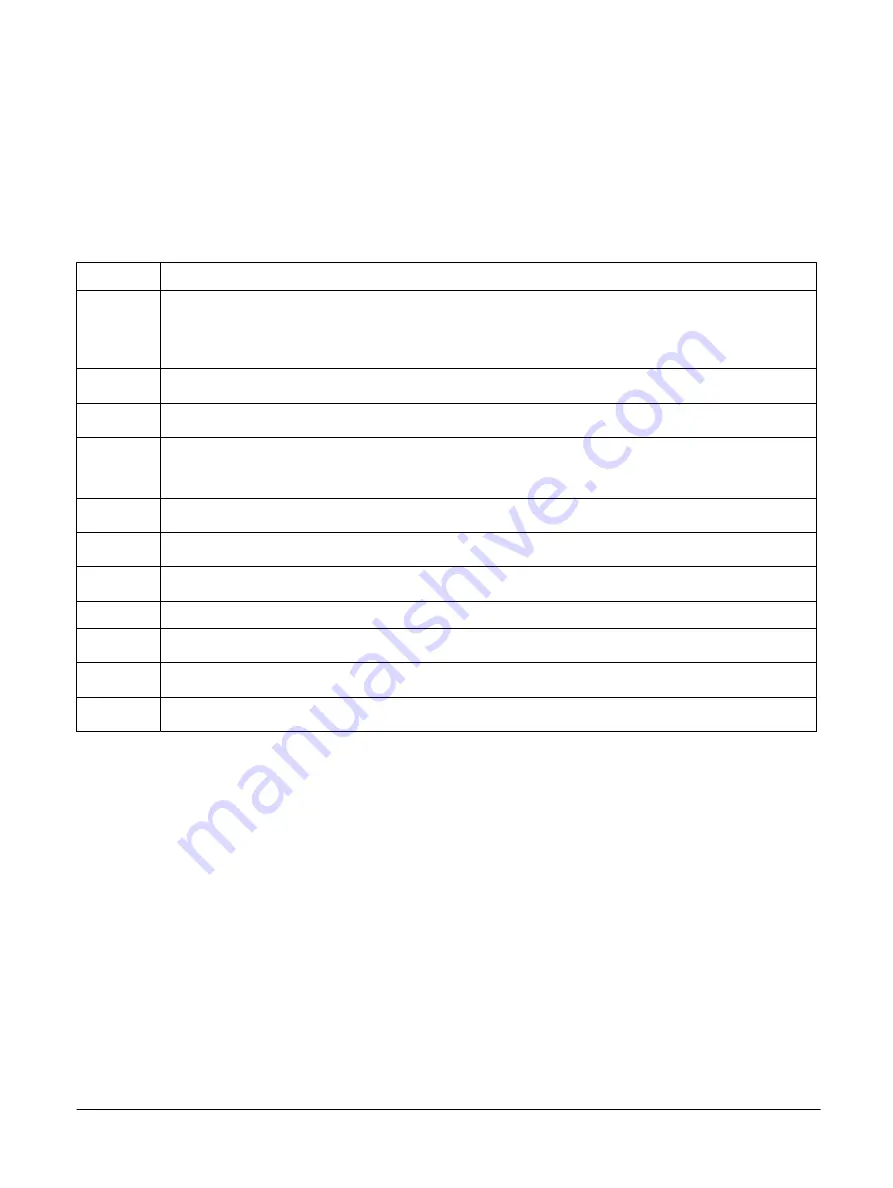

The following table shows the System instructions for cache and maintenance operations in AArch64

state.

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

for more

information about these operations.

Table B2-5 AArch64 cache maintenance operations

Name

Description

IC IALLUIS

Instruction cache invalidate all to PoU Inner Shareable

PoU = Point of Unification. PoU is set by the

BROADCASTINNER

signal and can be in the L1 data cache or outside

of the processor, in which case PoU is dependent on the external memory system.

IC IALLU

Instruction cache invalidate all to PoU

IC IVAU

Instruction cache invalidate by

virtual address

(VA) to PoU

DC IVAC

Data cache invalidate by VA to PoC

PoC = Point of Coherence. The PoC is always outside of the processor and depends on the external memory system.

DC ISW

Data cache invalidate by set/way

DC CSW

Data cache clean by set/way

DC CISW

Data cache clean and invalidate by set/way

DC ZVA

Data cache zero by VA

DC CVAC

Data cache clean by VA to PoC

DC CVAU

Data cache clean by VA to PoU

DC CIVAC

Data cache clean and invalidate by VA to PoC

B2 AArch64 system registers

B2.6 AArch64 Cache maintenance operations

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-369

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......