B1.67

Hyp System Control Register

The HSCTLR characteristics are:

Purpose

Provides top level control of the system operation in Hyp mode. This register provides Hyp

mode control of features controlled by the Banked SCTLR bits, and shows the values of the

non-Banked SCTLR bits.

Usage constraints

This register is accessible as follows:

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

-

-

RW RW

-

Configurations

HSCTLR is architecturally mapped to AArch64 register SCTLR_EL2. See

Attributes

HSCTLR is a 32-bit register.

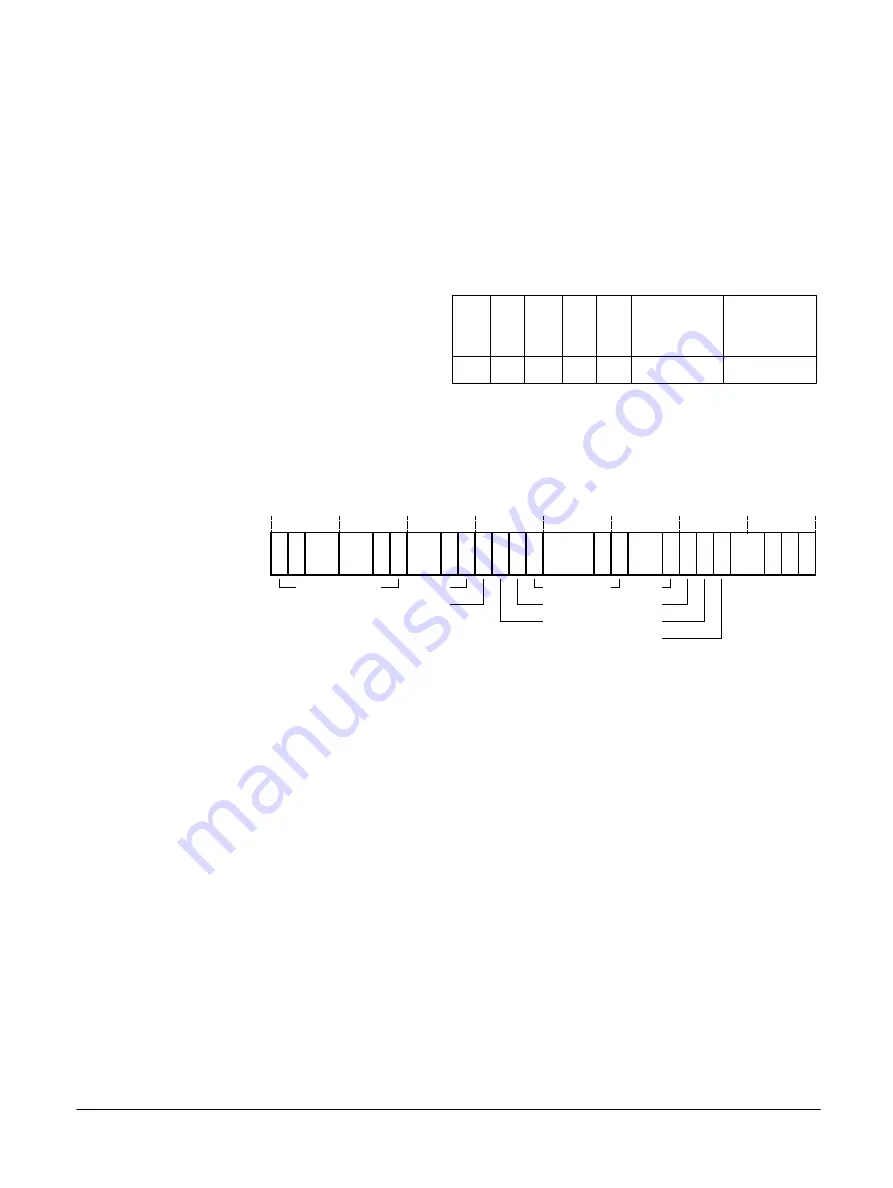

RES

0

RES

0

RES

1

RES

0

M

31 30 29

26 25 24

22 21 20 19 18

13 12 11

7 6

3 2 1 0

TE

RES

1

EE

FI

I

RES

1 C A

WXN

RES

0

RES

0

9

RES

0

SED

8

ITD

RES

1

5 4

CP15BEN

RES

0

27

28

23

17 16 15 14

10

RES

1

RES

1

RES

0

Figure B1-23 HSCTLR bit assignments

[31]

Reserved,

RES0

.

TE, [30]

Thumb Exception enable. This bit controls whether exceptions taken in Hyp mode are taken in

A32 or T32 state:

0

Exceptions taken in A32 state.

1

Exceptions taken in T32 state.

[29:28]

Reserved,

RES1

.

[27:26]

Reserved,

RES0

.

EE, [25]

Exception Endianness. The value of this bit defines the value of the CPSR.E bit on entry to an

exception vector, including reset. This value also indicates the endianness of the translation table

data for translation table lookups:

0

Little endian.

B1 AArch32 system registers

B1.67 Hyp System Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-254

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......