A.14

Debug signals

The processor has the following debug signals.

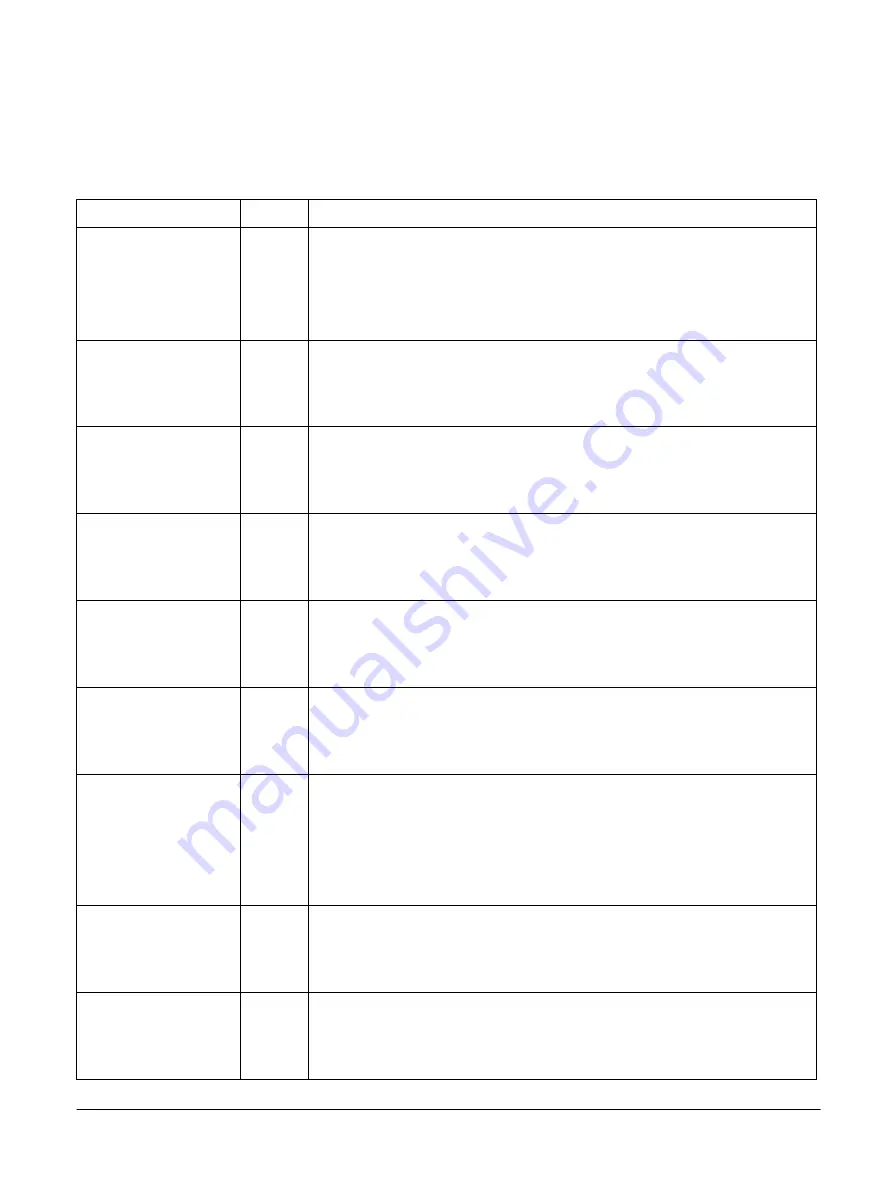

Table A-42 Debug signals

Signal

Direction Description

DBGROMADDR[39:12]

Input

Debug ROM base address.

Specifies bits[39:12] of the ROM table physical address.

If the address cannot be determined, tie this signal LOW.

This signal is sampled only during processor reset.

DBGROMADDRV

Input

Debug ROM base address valid.

If the debug ROM address cannot be determined, tie this signal LOW.

This signal is sampled only during processor reset.

DBGACK[CN:0]

Output

Debug acknowledge:

0

External debug request not acknowledged.

1

External debug request acknowledged.

nCOMMIRQ[CN:0]

Output

Communications channel receive or transmit interrupt request

0

Request interrupt.

1

No interrupt request.

COMMRX[CN:0]

Output

Communications channel receive. Receive portion of Data Transfer Register full flag:

0

Empty.

1

Full.

COMMTX[CN:0]

Output

Communication transmit channel. Transmit portion of Data Transfer Register empty flag:

0

Full.

1

Empty.

EDBGRQ[CN:0]

Input

External debug request:

0

No external debug request.

1

External debug request.

The processor treats the

EDBGRQ

input as level-sensitive. The

EDBGRQ

input must be

asserted until the processor asserts

DBGACK.

DBGEN[CN:0]

Input

Invasive debug enable:

0

Not enabled.

1

Enabled.

NIDEN[CN:0]

Input

Non-invasive debug enable:

0

Not enabled.

1

Enabled.

A Signal Descriptions

A.14 Debug signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-A-871

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......