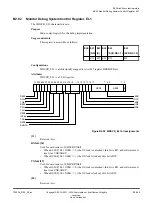

RXO, [27]

Used for save/restore of EDSCR.RXO.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

TXU, [26]

Used for save/restore of EDSCR.TXU.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

[25:24]

Reserved,

RES0

.

INTdis, [23:22]

Used for save/restore of EDSCR.INTdis.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

TDA, [21]

Used for save/restore of EDSCR.TDA.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

[20:19]

Reserved,

RES0

.

[18:16]

Reserved, RAZ/WI. Hardware must implement this as RAZ/WI. Software must not rely on this

property as the behavior of reserved values might change in a future revision of the architecture.

MDE, [15]

Monitor debug events. Enable Breakpoint, Watchpoint, and Vector catch debug exceptions.

0

Breakpoint, Watchpoint, and Vector catch debug exceptions disabled.

1

Breakpoint, Watchpoint, and Vector catch debug exceptions enabled.

When this register has an architecturally-defined reset value, this field resets to a value that is

architecturally UNKNOWN on Warm reset.

HDE, [14]

Used for save/restore of EDSCR.HDE.

• When OSLSR_EL1.OSLK == 0 (the OS lock is unlocked), this bit is RO. Software must

treat it as UNKNOWN and use an SBZP policy for writes.

• When OSLSR_EL1.OSLK == 1 (the OS lock is locked), this bit is RW.

KDE, [13]

Local (kernel) debug enable. If EL

D

is using AArch64, enable Software debug events within

EL

D

. Permitted values are:

0

Software debug events, other than Software breakpoint instructions, disabled within EL

D

.

1

Software debug events enabled within EL

D

.

RES0

if EL

D

is using AArch32.

B2 AArch64 system registers

B2.82 Monitor Debug System Control Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-507

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......