Defines Device memory, and Inner cacheability. Must be interpreted in conjunction with AttrH.

The possible values are:

0b0000

Device (nGnRnE) memory if AttrH is

0b0000

. Otherwise this value is reserved.

0b0100

Device (not nGnRnE) memory if AttrH is

0b0000

. Otherwise, Normal memory, Inner

Non-cacheable.

0b1000

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Through

Cacheable.

0b1001

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Through

Cacheable, Inner Write-Allocate.

0b1010

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Through

Cacheable, Inner Read-Allocate.

0b1011

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Through

Cacheable, Inner Write-Allocate, Inner Read-Allocate.

0b1100

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Back

Cacheable.

0b1101

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Back

Cacheable, Inner Write-Allocate.

0b1110

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Back

Cacheable, Inner Read-Allocate.

0b1111

Reserved if AttrH is

0b0000

. Otherwise, Normal memory, Inner Write-Through

Cacheable, Inner Write-Allocate, Inner Read-Allocate.

All other values are reserved.

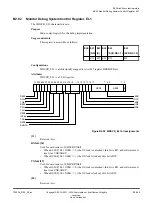

[55:48]

Reserved,

RES0

.

PA, [47:12]

Physical address. The Physical Address corresponding to the supplied Virtual Address. Returns

address bits[47:12].

[11]

Reserved,

RES1

.

[10]

Reserved,

RES0

.

NS, [9]

Non-secure. The NS attribute for a translation table entry read from Secure state.

This bit is

UNKNOWN

for a translation table entry from Non-secure state.

SHA, [8:7]

Shareability attribute for the Physical Address returned from a translation table entry. The

possible values are:

0b00

Non-shareable.

0b01

Reserved.

0b10

Outer Shareable

0b11

Inner Shareable.

Takes the value of

0b10

for:

• Any type of device memory.

• Normal memory with both Inner Non-cacheable and Outer-cacheable attributes.

B2 AArch64 system registers

B2.85 Physical Address Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-515

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......