A5.7

About cache protection

The processor protects against soft errors that result in a RAM bitcell temporarily holding the incorrect

value, by writing a new value to the RAM to correct the error. If the error is a hard error that is not

corrected by writing to the RAM, for example a physical defect in the RAM, then the processor might

get into a livelock because it continually detects and then tries to correct the error.

Some RAMs have

Single Error Detect

(SED) capability, others have

Single Error Correct, Double Error

Detect

(SECDED) capability. The L1 data cache dirty RAM is

Single Error Detect, Single Error Correct

(SEDSEC). The processor can make progress and remain functionally correct when there is a single bit

error in any RAM. If there are multiple single bit errors in different RAMs or within different protection

granules within the same RAM, then the processor also remains functionally correct.

If there is a double bit error in a single RAM within the same protection granule, then the behavior

depends on the RAM:

• For RAMs with SECDED capability, the processor detects and reports the error. If the error is in a

cache line that contains dirty data, that data might be lost, which then causes data corruption.

• For RAMs with only SED, the processor does not detect a double bit error. This might cause data

corruption.

If there are three or more bit errors the processor might or might not detect the errors, depending on the

RAM and the position of the errors within the RAM.

The cache protection feature of the processor has a minimal performance impact when no errors are

present. When the processor detects an error, it stalls the access that caused the error while it corrects the

error. When the correction is complete, the access either continues with the corrected data or is retried. If

the access is retried, it either hits in the cache again with the corrected data or misses in the cache and re-

fetches the data from a lower level cache or from main memory.

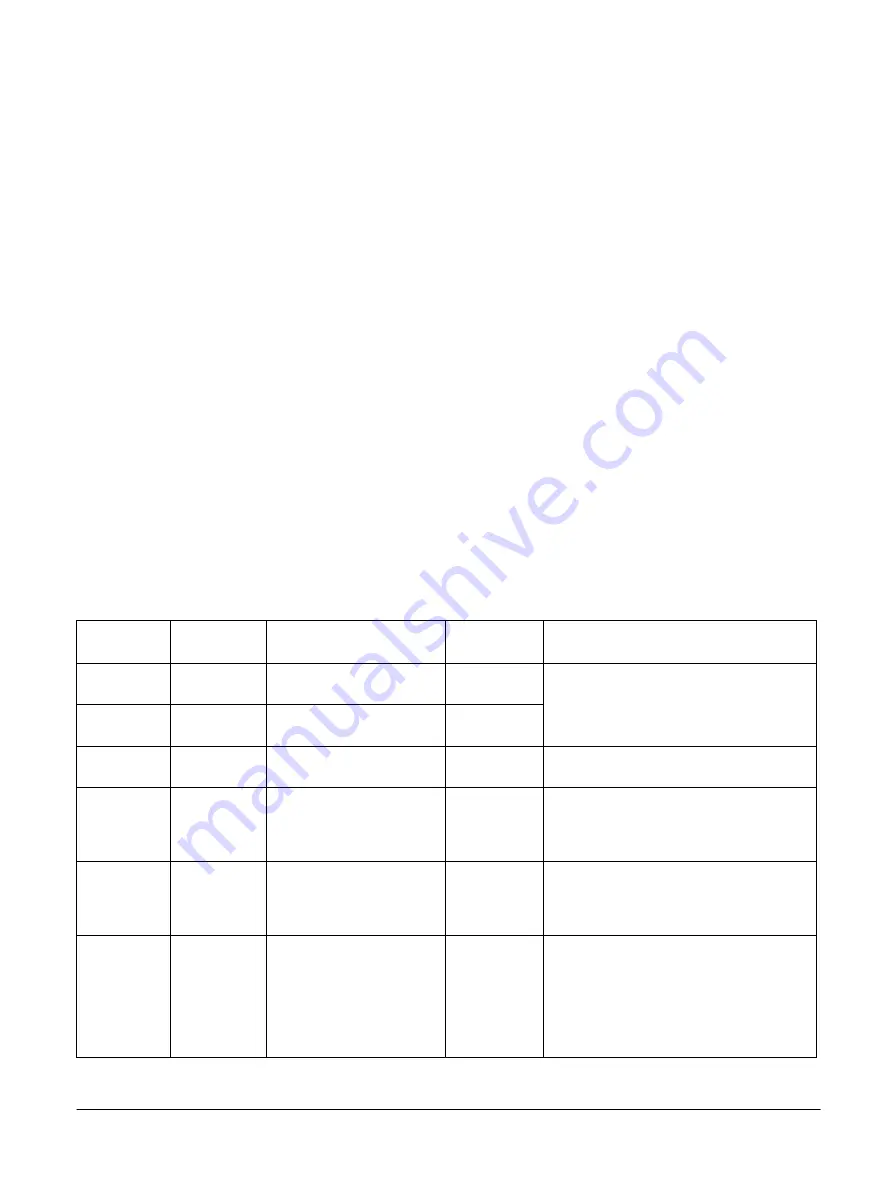

Table A5-2 Cache protection behavior of each RAM

RAM

Protection

type

Configuration option

Protection

granule

Correction behavior

L1 instruction

cache tag

Parity, SED

CPU_CACHE_PROTECTION 31 bits

The processor invalidates both lines in the cache

set then refetches the requested line from the L2

cache or external memory.

L1 instruction

cache data

Parity, SED

CPU_CACHE_PROTECTION 18 bits

TLB

Parity, SED

CPU_CACHE_PROTECTION 31 bits or 51

bits

The processor invalidates the entry and starts a

new pagewalk to refetch it.

L1 data cache

tag

Parity, SED

CPU_CACHE_PROTECTION 32 bits

The processor cleans the line and invalidates it

from the L1 cache. It uses SCU duplicate tags to

get the correct address. It refetches the line from

the L2 cache or external memory.

L1 data cache

data

ECC, SECDED CPU_CACHE_PROTECTION 32 bits

The processor cleans the line and invalidates it

from the L1 cache. It corrects single bit errors as

part of the eviction. It refetches the line from the

L2 cache or external memory.

L1 data cache

dirty

Parity,

SEDSEC

CPU_CACHE_PROTECTION 1 bit

The processor cleans the line and invalidates it

from the L1 cache. It corrects single bit errors as

part of the eviction.

Only the dirty bit is protected. The other bits are

performance hints, therefore do not cause a

functional failure if they are incorrect.

A5 Cache Behavior and Cache Protection

A5.7 About cache protection

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A5-84

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......