B1.19

64-bit registers

The processor can access 64-bit wide CP15 system registers in AArch32 state.

The following table shows the 64-bit wide CP15 system registers, accessed by the

MCRR

and

MRRC

instructions. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

for

more information.

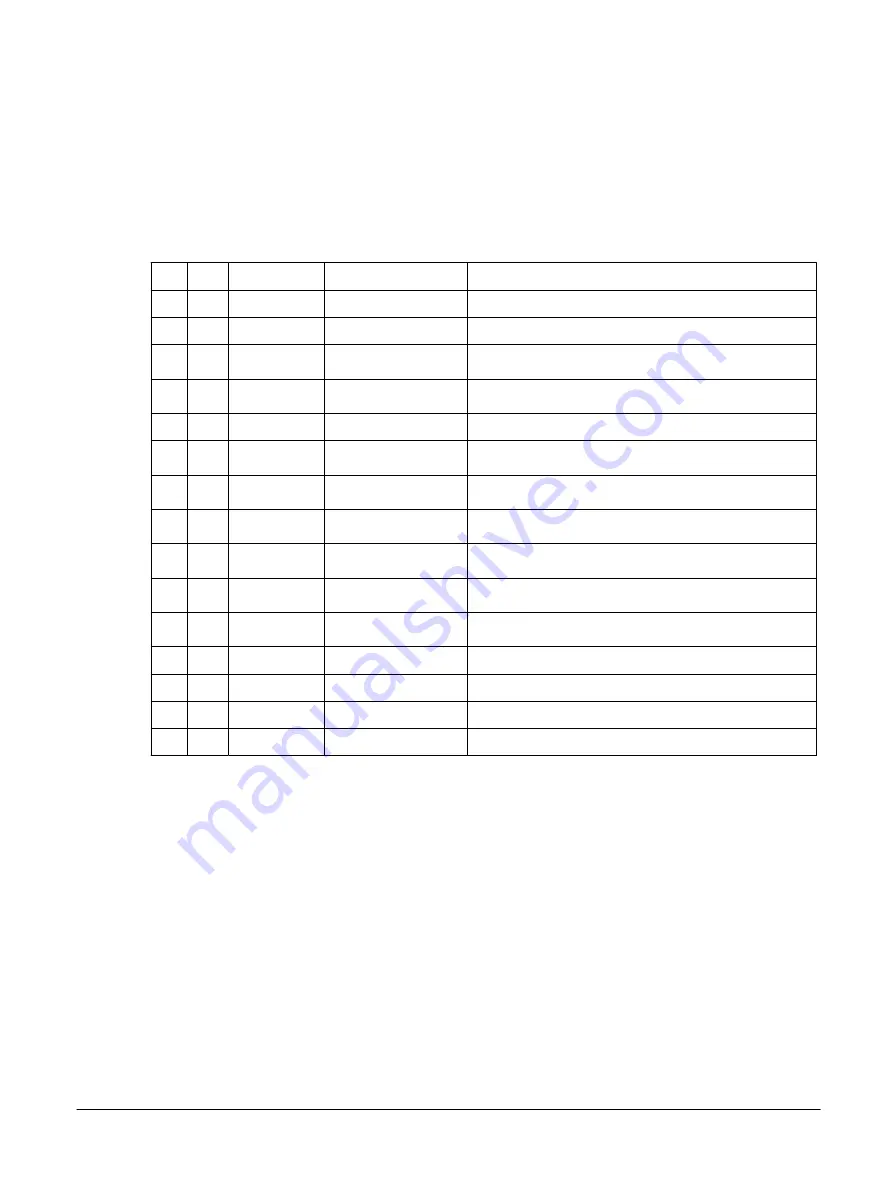

Table B1-18 64-bit register summary

Op1 CRm Name

Reset

Description

0

c2

TTBR0

UNK

Translation Table Base Register 0

1

c2

TTBR1

UNK

Translation Table Base Register 1

4

c2

HTTBR

UNK

Hyp Translation Table Base Register

6

c2

VTTBR

UNK

Virtualization Translation Table Base Register

0

c7

PAR

UNK

B1.100 Physical Address Register

0

c14

CNTPCT

UNK

Physical Timer Count Register

1

c14

CNTVCT

UNK

Virtual Timer Count Register

2

c14

CNTP_CVAL

UNK

Physical Timer CompareValue Register

3

c14

CNTV_CVAL

UNK

Virtual Timer CompareValue Register

4

c14

CNTVOFF

UNK

Virtual Timer Offset Register

6

c14

CNTHP_CVAL UNK

Physical Timer CompareValue Register

0

c15

CPUACTLR

0x00000000090CA000

B1.42 CPU Auxiliary Control Register

1

c15

CPUECTLR

0x0000000000000000

B1.43 CPU Extended Control Register

2

c15

CPUMERRSR -

B1.44 CPU Memory Error Syndrome Register

3

c15

L2MERRSR

-

B1.94 L2 Memory Error Syndrome Register

B1 AArch32 system registers

B1.19 64-bit registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-175

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......