B2.75

L2 Extended Control Register, EL1

The L2ECTLR_EL1 characteristics are:

Purpose

Provides additional

IMPLEMENTATION DEFINED

control options for the L2 memory system. This

register is used for dynamically changing, but implementation specific, control bits.

Usage constraints

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW RW RW

RW

The L2ECTLR_EL1 can be written dynamically.

Configurations

L2ECTLR_EL1 is mapped to the AArch32 L2ECTLR register. See

There is one copy of this register that is used in both Secure and Non-secure states.

There is one L2ECTLR_EL1 for the Cortex

‑

A35 processor.

Attributes

L2ECTLR_EL1 is a 32-bit register.

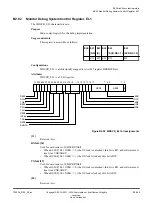

31

0

30

28

RES

0

RES

0

29

L2 internal asynchronous error

1

2

3

AXI, ACE, or CHI asynchronous error

L2 dynamic retention control

Figure B2-47 L2ECTLR_EL1 bit assignments

[31]

Reserved,

RES0

.

L2 internal asynchronous error, [30]

L2 internal asynchronous error caused by L2 RAM double-bit ECC error. The possible values

are:

0

No pending asynchronous error. This is the reset value.

1

An asynchronous error has occurred.

A write of

0

clears this bit and drives

nINTERRIRQ

HIGH. A write of

1

is ignored.

AXI, ACE, or CHI asynchronous error, [29]

AXI, ACE, or CHI asynchronous error indication. The possible values are:

0

No pending asynchronous error.

1

An asynchronous error has occurred.

A write of

0

clears this bit and drives

nEXTERRIRQ

HIGH. A write of

1

is ignored.

B2 AArch64 system registers

B2.75 L2 Extended Control Register, EL1

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-491

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......