B3.4

Virtual interface control register summary

The virtual interface control registers are management registers. Configuration software on the

Cortex

‑

A35 processor must ensure they are accessible only by a hypervisor, or similar software.

The following table describes the registers for the virtual interface control registers. All these registers

are word-accessible. Registers not described in this table are

RES0

. See the

Arm

®

Generic Interrupt

Controller Architecture Specification

for more information.

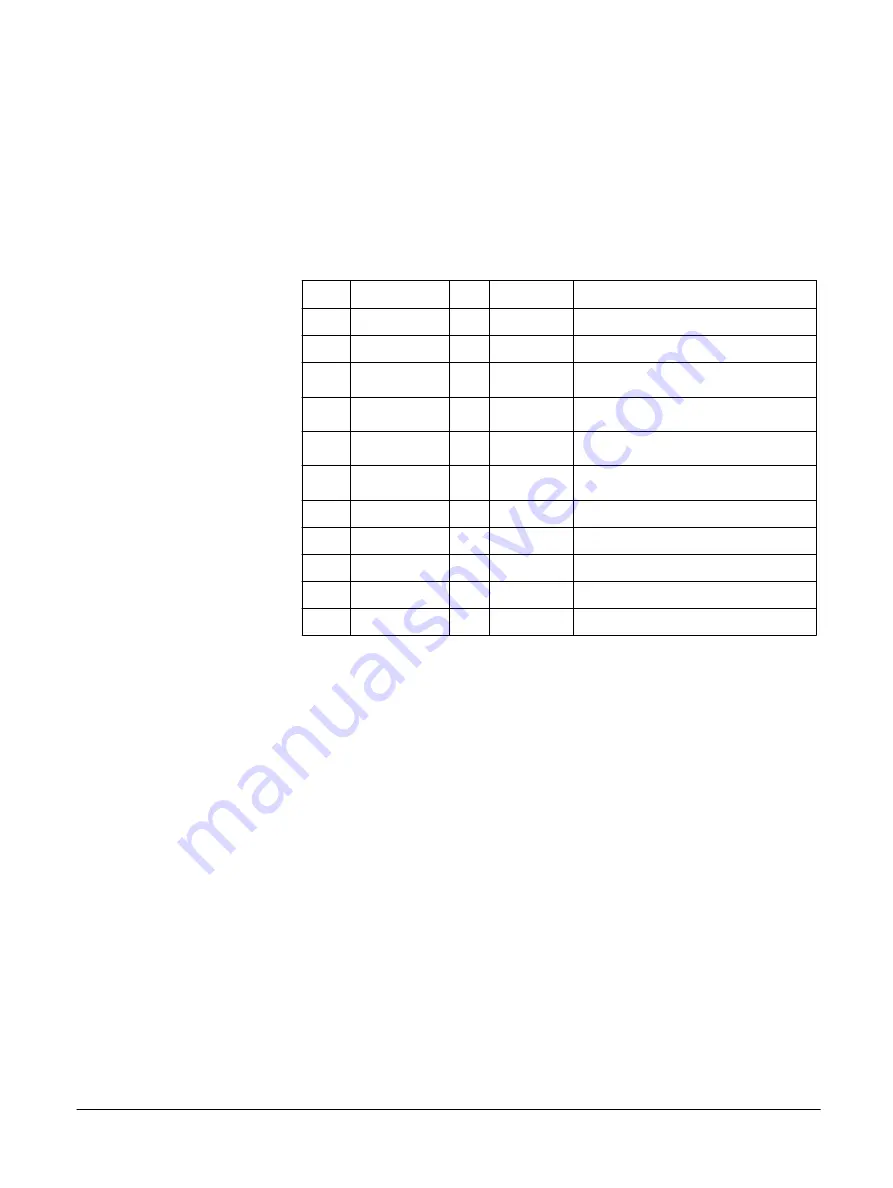

Table B3-3 Virtual interface control register summary

Offset Name

Type Reset

Description

0x000

GICH_HCR

RW

0x00000000

Hypervisor Control Register

0x004

GICH_VTR

RO

0x90000003

0x008

GICH_VMCR

RW

0x004C0000

Virtual Machine Control Register

0x010

GICH_MISR

RO

0x00000000

Maintenance Interrupt Status Register

0x020

GICH_EISR0

RO

0x00000000

End of Interrupt Status Registers

0x030

GICH_ELRSR0 RO

0x0000000F

Empty List Register Status Registers

0x0F0

GICH_APR0

RW

0x00000000

Active Priorities Register

0x100

GICH_LR0

RW

0x00000000

List Register 0

0x104

GICH_LR1

RW

0x00000000

List Register 1

0x108

GICH_LR2

RW

0x00000000

List Register 2

0x10C

GICH_LR3

RW

0x00000000

List Register 3

B3 GIC registers

B3.4 Virtual interface control register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B3-563

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......