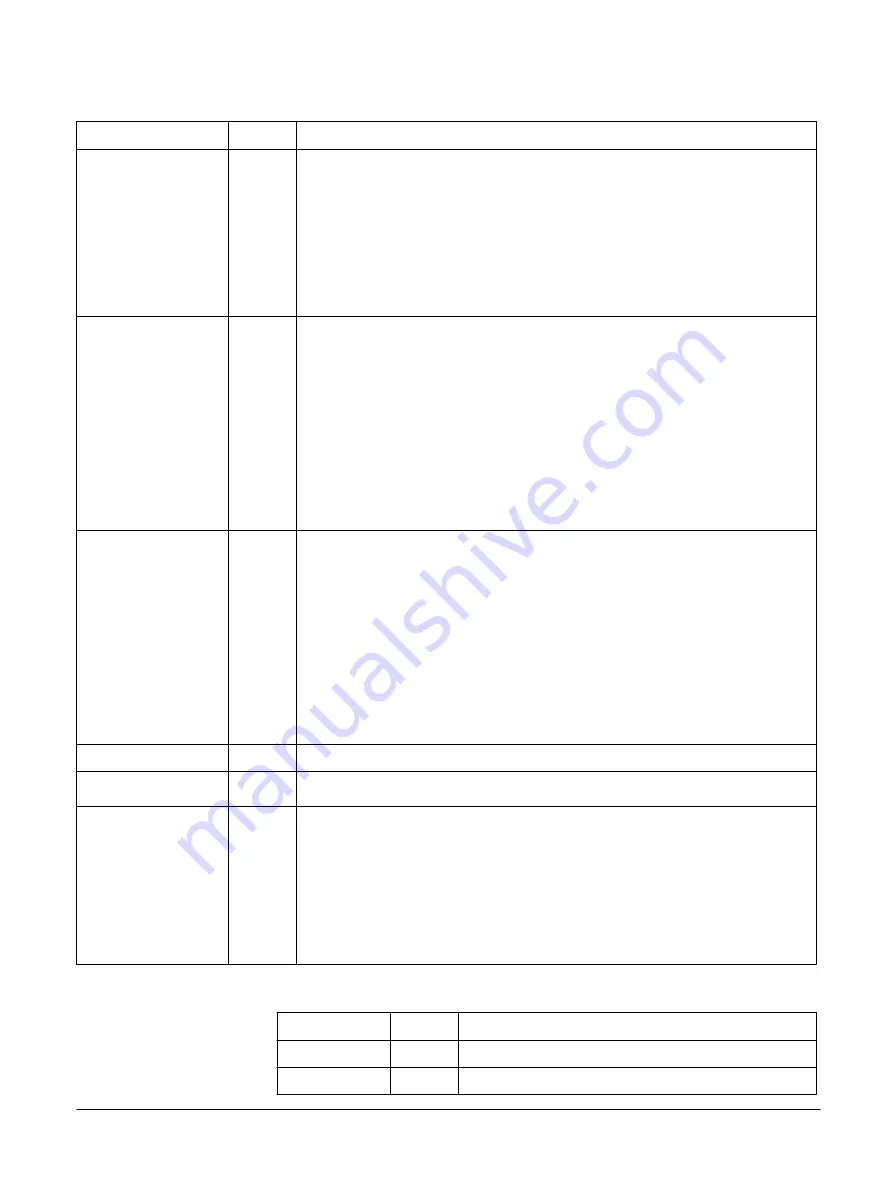

Table A-4 GIC signals (continued)

Signal

Direction Description

nVIRQ[CN:0]

Input

Virtual IRQ request. Active-LOW, level sensitive, asynchronous interrupt request:

0

Activate interrupt.

1

Do not activate interrupt.

The processor treats

nVIRQ

as level-sensitive.

nVIRQ

must be asserted until the processor

acknowledges the interrupt. If the GIC is enabled by tying

GICCDISABLE

LOW,

nVIRQ

must be tied off to HIGH. If the GIC is disabled by tying

GICCDISABLE

HIGH,

nVIRQ

can be driven by an external GIC in the SoC.

nVSEI[CN:0]

Input

Virtual System Error Interrupt request. Active-LOW, edge sensitive:

0

Activate virtual SEI request.

1

Do not activate virtual SEI request.

The processor treats

nVSEI

as edge-sensitive. The

nVSEI

signal must be sent as a pulse to

the processor.

Asserting

nVSEI

causes one of the following to occur:

•

Asynchronous Data Abort, if taken to AArch32. The DFSR.FS field is set to indicate an

Asynchronous External Abort.

•

SError interrupt, if taken to AArch64. The ESR_EL1.ISS field is set.

nREI[CN:0]

Input

RAM Error Interrupt request. Active-LOW, edge sensitive:

0

Activate REI request. Reports an asynchronous RAM error in the system.

1

Do not activate REI request.

The processor treats

nREI

as edge-sensitive. The

nREI

signal must be sent as a pulse to the

processor.

Asserting the

nREI

input causes one of the following to occur:

•

Asynchronous Data Abort, if taken to AArch32. The DFSR.FS field is set to indicate an

Asynchronous parity error on memory access.

•

SError interrupt, if taken to AArch64. The ESR_ELx.ISS field is set.

nVCPUMNTIRQ[CN:0]

Output

Virtual CPU interface maintenance interrupt PPI output.

PERIPHBASE[39:18]

Input

Specifies the base address for the GIC registers. This value is sampled into CBAR at reset.

GICCDISABLE

Input

Globally disables the GIC CPU interface logic and routes the external signals directly to the

processor:

0

Enable the GIC CPU interface logic.

1

Disable the GIC CPU interface logic and route the legacy

nIRQ

,

nFIQ

,

nVIRQ

,

and

nVFIQ

signals directly to the processor. Drive this signal HIGH when you are

using a legacy interrupt controller such as the GIC-400 which does not support

GICv3 or GICv4.

Table A-5 AXI4 Stream Protocol signals for messages from the Distributor to the GIC CPU Interface

Signal

Direction Description

ICDTVALID

Input

Indicates that the master is driving a valid transfer.

ICDTREADY

Output

Indicates that the slave can accept a transfer in the current cycle.

A Signal Descriptions

A.5 GIC signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

Appx-A-853

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......