ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

131

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

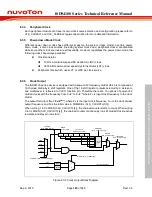

6.2.14 System Control Register

The Cortex

®

-M4 status and operation mode control are managed by System Control Registers.

These registers also manage CPUID, Cortex

®

-M4 interrupt priority and Cortex

®

-M4 power

management.

For more detailed information, please refer to the “

ARM

®

Cortex™-M4 Technical Reference Manual

”

and “

ARM

®

v6-M Architecture Reference Manual

”.

R:

read only,

W:

write only,

R/W:

both read and write

Register

Offset

R/W Description

Reset Value

SCR Base Address:

SCS_BA = 0xE000_E000

ICSR

0xD04

R/W Interrupt Control and State Register

0x0000_0000

AIRCR

0xD0C

R/W Application Interrupt and Reset Control Register

0xFA05_0000

SCR

0xD10

R/W System Control Register

0x0000_0000

SHPR1

0xD18

R/W System Handler Priority Register 1

0x0000_0000

SHPR2

0xD1C

R/W System Handler Priority Register 2

0x0000_0000

SHPR3

0xD20

R/W System Handler Priority Register 3

0x0000_0000

Note:

1.

Any register not listed here is reserved and must not be written. The result of a read operation on these bits is undefined.

2.

The reserved register fields that listed in register description must be written to their reset value. Writing reserved fields with

other than reset values may produce undefined results.