ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

732

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

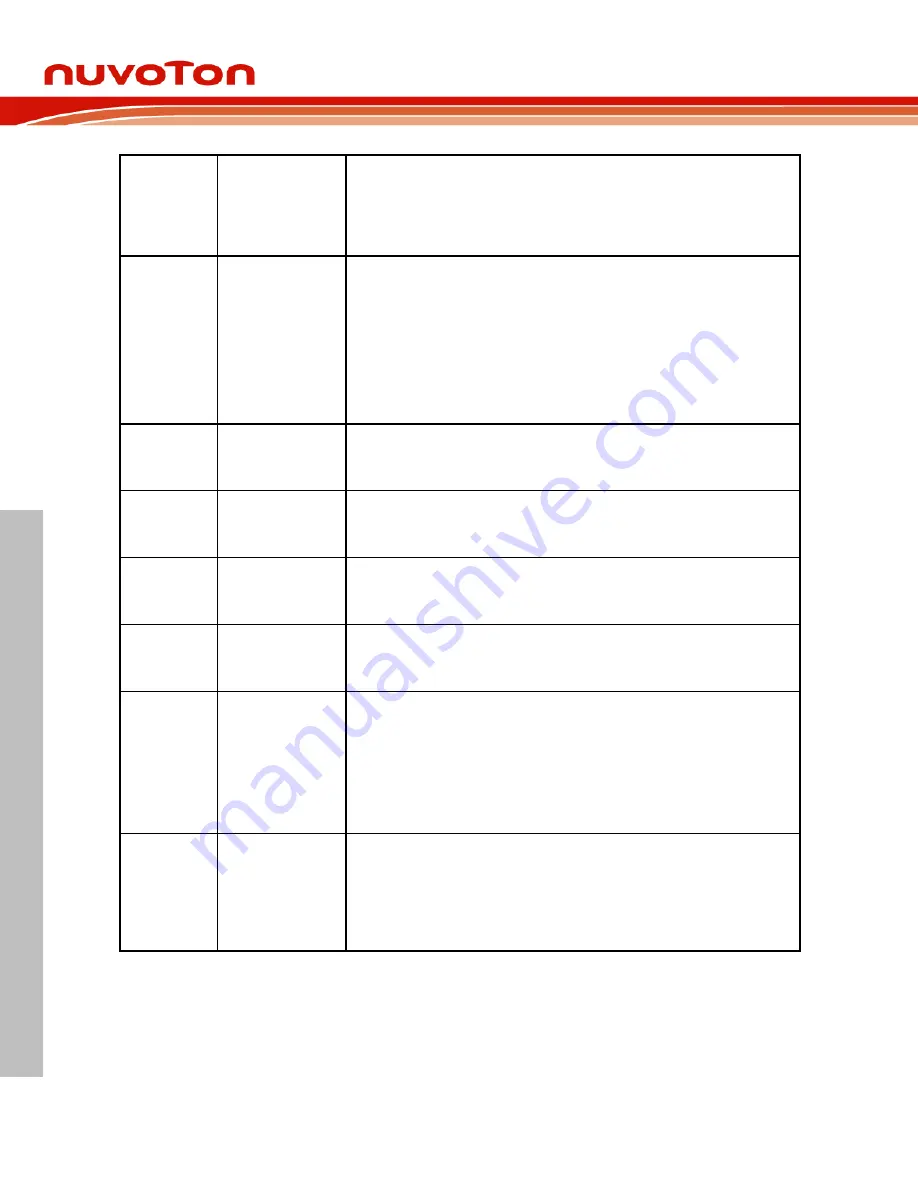

[7]

TXUFIEN

TX Underflow Interrupt Enable Bit

When TX underflow event occurs in Slave mode, TXUFIF (SPIn_STATUS[19]) will be

set to 1. This bit is used to enable the TX underflow interrupt.

0 = Slave TX underflow interrupt Disabled.

1 = Slave TX underflow interrupt Enabled.

[6]

TXUFPOL

TX Underflow Data Polarity

0 = The SPI data out is keep 0 if there is TX underflow event in Slave mode.

1 = The SPI data out is keep 1 if there is TX underflow event in Slave mode.

Note1:

The TX underflow event occurs if there is no any data in TX FIFO when the

slave selection signal is active.

Note2:

This bit should be set as 0 in I

2

S mode.

Note3:

When TX underflow event occurs, SPIn_MISO (n=1, 2) pin state will be

determined by this setting even though TX FIFO is not empty afterward. Data stored

in TX FIFO will be sent through SPIn_MISO (n=1, 2) pin in the next transfer frame.

[5]

RXOVIEN

Receive FIFO Overrun Interrupt Enable Bit

0 = Receive FIFO overrun interrupt Disabled.

1 = Receive FIFO overrun interrupt Enabled.

[4]

RXTOIEN

Slave Receive Time-out Interrupt Enable Bit

0 = Receive time-out interrupt Disabled.

1 = Receive time-out interrupt Enabled.

[3]

TXTHIEN

Transmit FIFO Threshold Interrupt Enable Bit

0 = TX FIFO threshold interrupt Disabled.

1 = TX FIFO threshold interrupt Enabled.

[2]

RXTHIEN

Receive FIFO Threshold Interrupt Enable Bit

0 = RX FIFO threshold interrupt Disabled.

1 = RX FIFO threshold interrupt Enabled.

[1]

TXRST

Transmit Reset

0 = No effect.

1 = Reset transmit FIFO pointer and transmit circuit. The TXFULL bit will be cleared

to 0 and the TXEMPTY bit will be set to 1. This bit will be cleared to 0 by hardware

about 3 system clock 2 peripheral clock cycles after it is set to 1. User can

read TXRXRST (SPIn_STATUS[23]) to check if reset is accomplished or not.

Note:

If TX underflow event occurs in SPI Slave mode, this bit can be used to make

SPI return to idle state.

[0]

RXRST

Receive Reset

0 = No effect.

1 = Reset receive FIFO pointer and receive circuit. The RXFULL bit will be cleared to

0 and the RXEMPTY bit will be set to 1. This bit will be cleared to 0 by hardware about

3 system clock 2 peripheral clock cycles after it is set to 1. User can read

TXRXRST (SPIn_STATUS[23]) to check if reset is accomplished or not.