ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

154

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

1 = SPI1 clock Enabled.

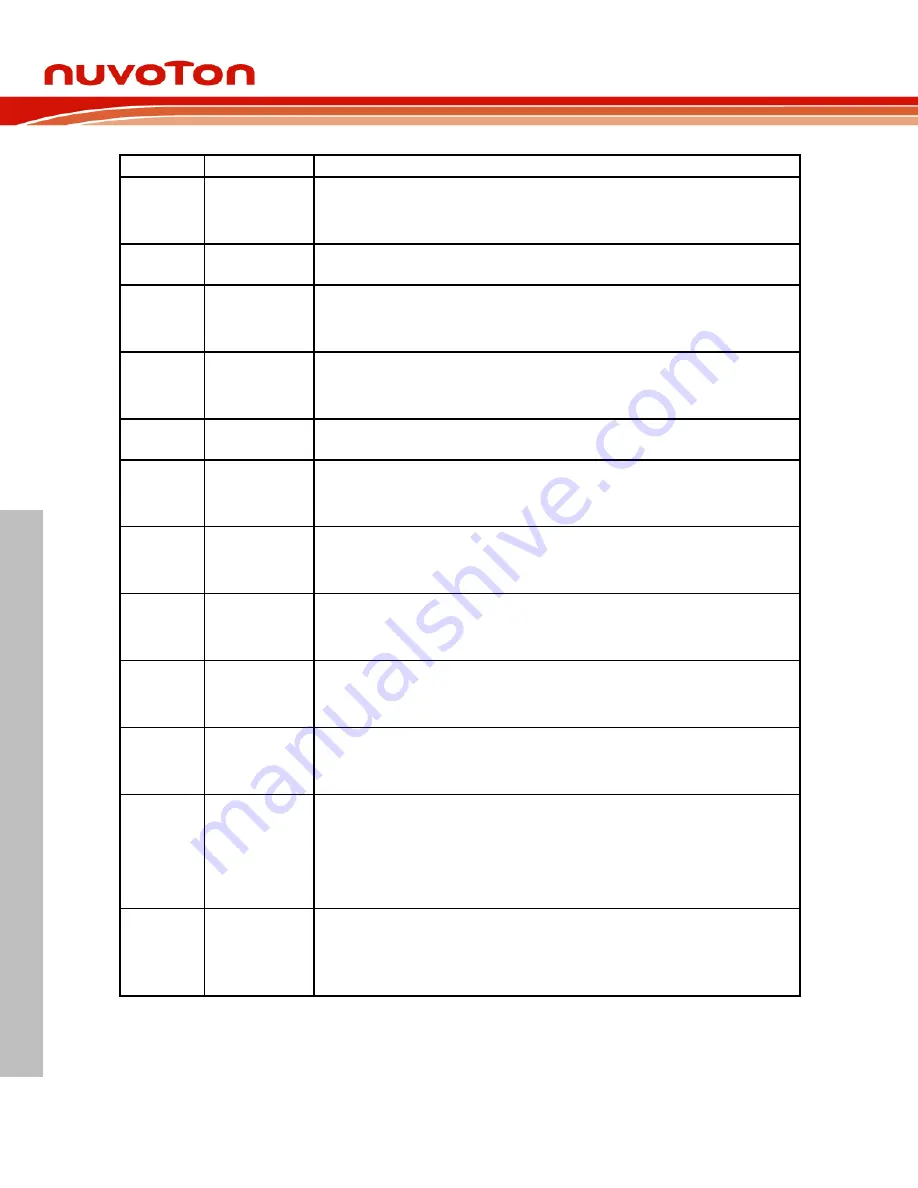

[12]

SPI0CKEN

SPI0 Clock Enable Bit

0 = SPI0 clock Disabled.

1 = SPI0 clock Enabled.

[11:10]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[9]

I2C1CKEN

I2C1 Clock Enable Bit

0 = I2C1 clock Disabled.

1 = I2C1 clock Enabled.

[8]

I2C0CKEN

I2C0 Clock Enable Bit

0 = I2C0 clock Disabled.

1 = I2C0 clock Enabled.

[7]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[6]

CLKOCKEN

CLKO Clock Enable Bit

0 = CLKO clock Disabled.

1 = CLKO clock Enabled.

[5]

TMR3CKEN

Timer3 Clock Enable Bit

0 = Timer3 clock Disabled.

1 = Timer3 clock Enabled.

[4]

TMR2CKEN

Timer2 Clock Enable Bit

0 = Timer2 clock Disabled.

1 = Timer2 clock Enabled.

[3]

TMR1CKEN

Timer1 Clock Enable Bit

0 = Timer1 clock Disabled.

1 = Timer1 clock Enabled.

[2]

TMR0CKEN

Timer0 Clock Enable Bit

0 = Timer0 clock Disabled.

1 = Timer0 clock Enabled.

[1]

RTCCKEN

Real-time-clock APB Interface Clock Enable Bit

This bit is used to control the RTC APB clock only. The RTC peripheral clock source is

selected from RTCSEL(CLK_CLKSEL3[8]). It can be selected to 32.768 kHz external low

speed crystal or 10 kHz internal low speed RC oscillator (LIRC).

0 = RTC clock Disabled.

1 = RTC clock Enabled.

[0]

WDTCKEN

Watchdog Timer Clock Enable Bit (Write Protected)

0 = Watchdog timer clock Disabled.

1 = Watchdog timer clock Enabled.

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.