ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

298

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

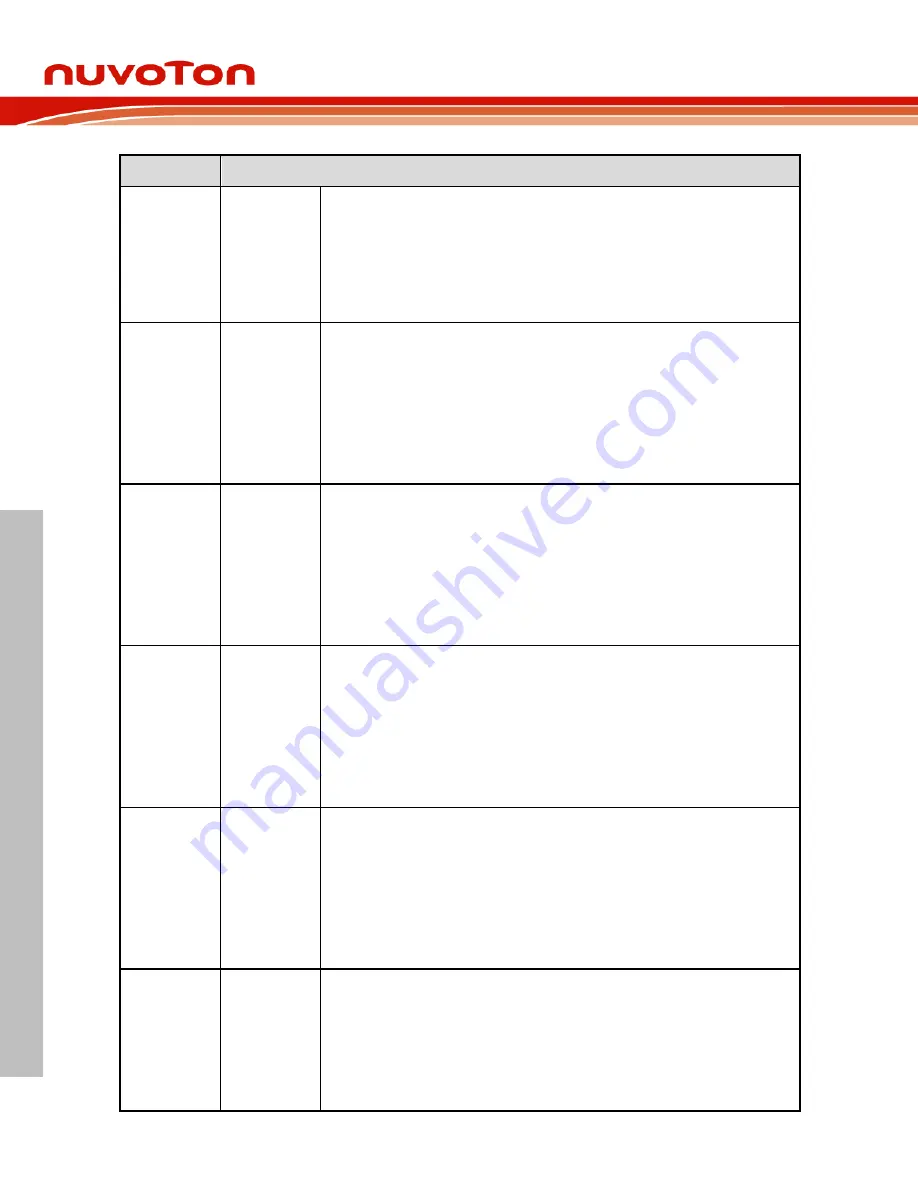

Bits

Description

This flag indicates whether channel 12 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 12 has no request.

1 = PDMA Channel 12 has a request.

Note:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing

current transfer.

[11]

REQSTS11

PDMA Channel 11 Request Status (Read Only)

This flag indicates whether channel 11 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 11 has no request.

1 = PDMA Channel 11 has a request.

Note:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing

current transfer.

[10]

REQSTS10

PDMA Channel 10 Request Status (Read Only)

This flag indicates whether channel 10 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 10 has no request.

1 = PDMA Channel 10 has a request.

Note:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing

current transfer.

[9]

REQSTS9

PDMA Channel 9 Request Status (Read Only)

This flag indicates whether channel 9 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 9 has no request.

1 = PDMA Channel 9 has a request.

Note1:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing

current transfer.

[8]

REQSTS8

PDMA Channel 8 Request Status (Read Only)

This flag indicates whether channel 8 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 8 has no request.

1 = PDMA Channel 8 has a request.

Note:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing

current transfer.

[7]

REQSTS7

PDMA Channel 7 Request Status (Read Only)

This flag indicates whether channel 7 have a request or not, no matter request from

software or peripheral. When PDMA controller finishes channel transfer, this bit will be

cleared automatically.

0 = PDMA Channel 7 has no request.

1 = PDMA Channel 7 has a request.

Note:

If user stops or resets each PDMA transfer by setting PDMA_STOP or

PDMA_CHRST register respectively, this bit will be cleared automatically after finishing