ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

156

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

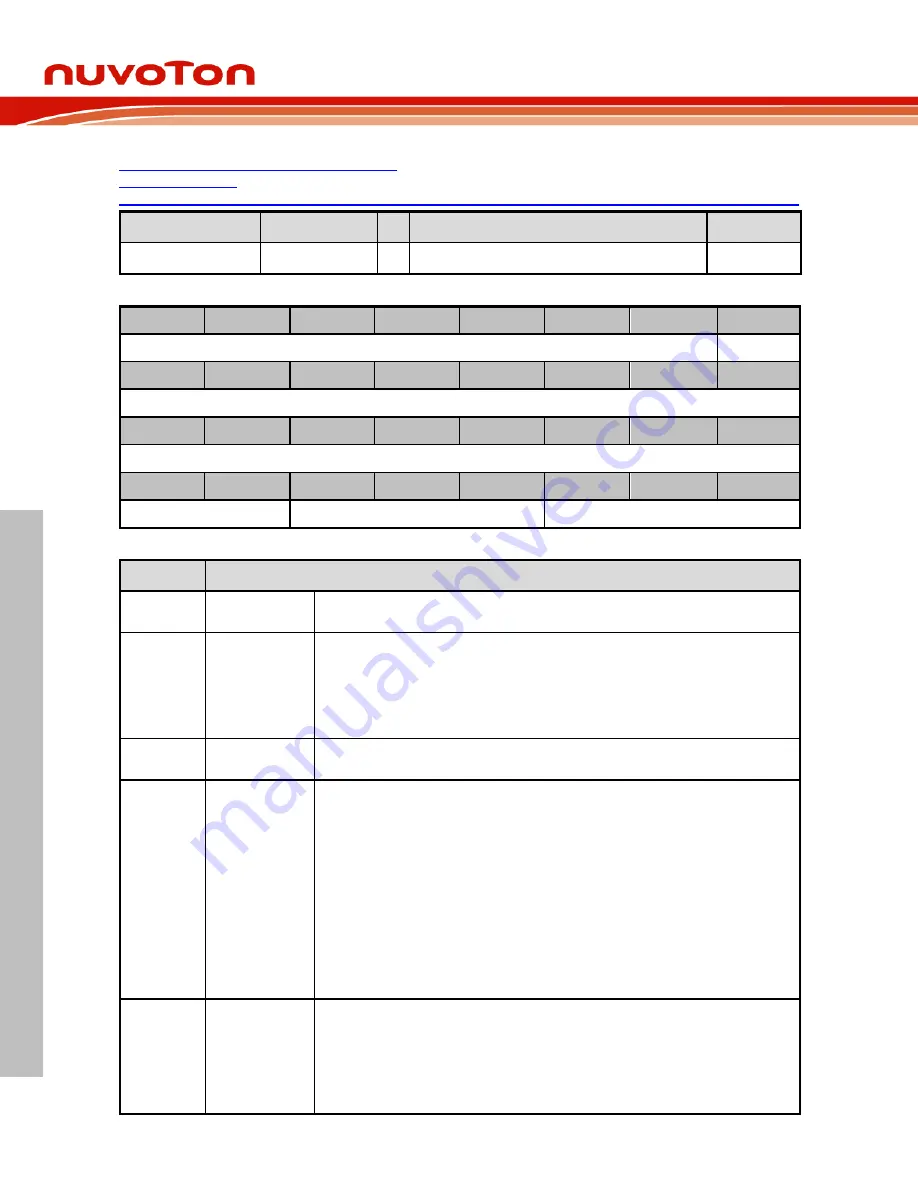

Clock Source Select Control Register 0

(CLK_CLKSEL0)

Register

Offset

R/W Description

Reset Value

CLK_CLKSEL0

0x10

R/W Clock Source Select Control Register 0

0x0000_003X

31

30

29

28

27

26

25

24

Reserved

HIRCFSEL

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved

STCLKSEL

HCLKSEL

Bits

Description

[31:25]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[24]

HIRCFSEL

Internal High Speed RC Oscillator Frequency Selection. (Write Protect)

Determines which trim setting to use for internal high speed RC oscillator.

0 = 49.152 MHz .

1 = 48.0 MHz.

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.

[23:6]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[5:3]

STCLKSEL

Cortex

®

-M4 SysTick Clock Source Selection (Write Protected)

If SYST_CTRL[2]=0, SysTick uses listed clock source below.

000 = Clock source from HXT.

001 = Clock source from LXT.

010 = Clock source from HXT/2.

011 = Clock source from HCLK/2.

111 = Clock source from HIRC/2.

Note1:

if SysTick clock source is not from HCLK (i.e. SYST_CTRL[2] = 0), SysTick clock

source must less than or equal to HCLK/2.

Note2:

The reset value of this field is 111b.

Note3:

This bit is write protected. Refer to the SYS_REGLCTL register.

[2:0]

HCLKSEL

HCLK Clock Source Selection (Write Protected)

Before clock switching, the related clock sources (both pre-select and new-select) must be

turned on and stable flag must be 1.

The default value is reloaded from the value of CFOSC (CONFIG0[26]) in user configuration

register of Flash controller by any reset. Therefore the default value is either 000b or 111b.

000 = Clock source from HXT.