ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

68

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

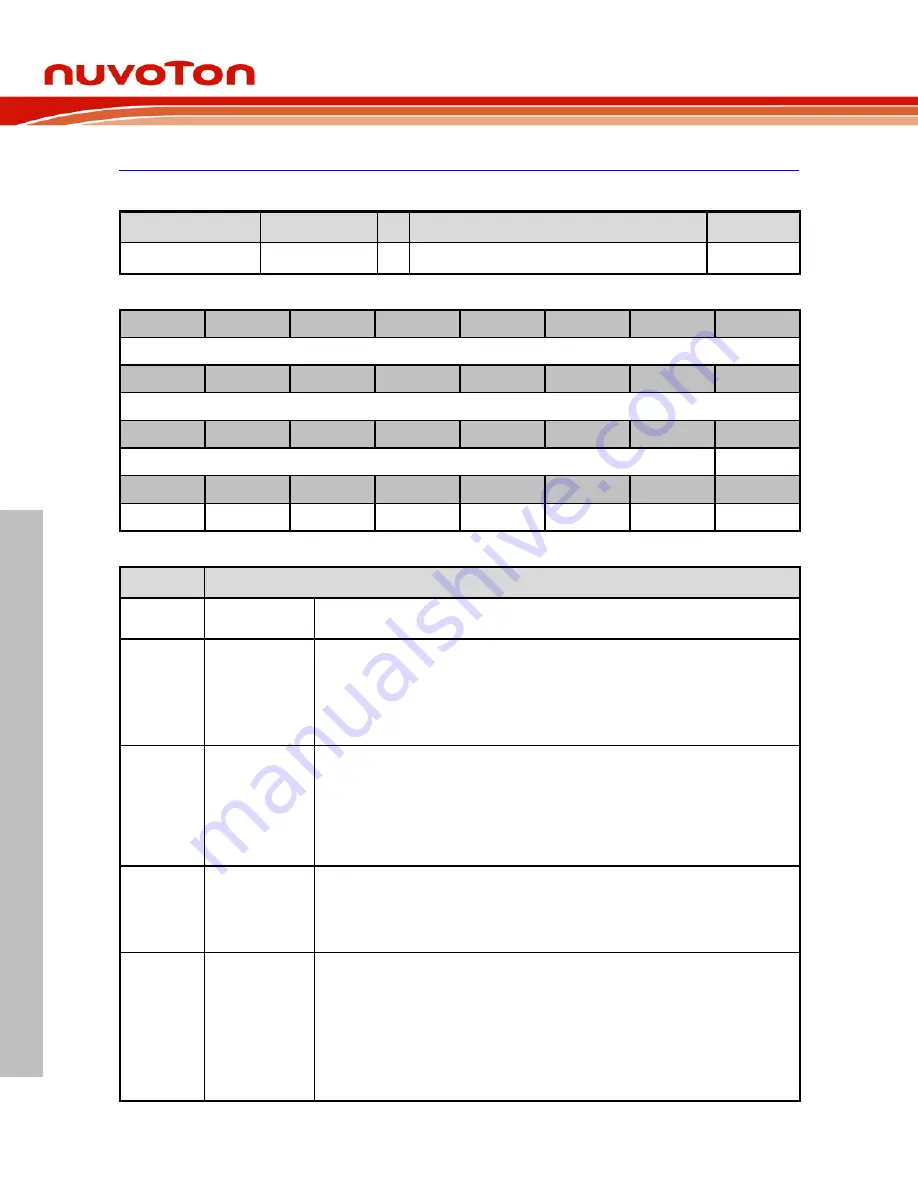

System Reset Status Register (SYS_RSTSTS)

This register provides specific information for software to identify this chip’s reset source from last

operation.

Register

Offset

R/W Description

Reset Value

SYS_RSTSTS

0x04

R/W System Reset Status Register

0x0000_0043

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

CPULKRF

7

6

5

4

3

2

1

0

CPURF

PMURF

SYSRF

BODRF

LVRF

WDTRF

PINRF

PORF

Bits

Description

[31:9]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[8]

CPULKRF

CPU Lockup Reset Flag

0 = No reset from CPU lockup occurred.

1 = The Cortex-M4 lockup occurred and chip is reset.

Note:

Write 1 to clear this bit to 0.

Note:

when ICE is connected, CPU lockup event sets this flag to 1 but will not reset chip.

[7]

CPURF

CPU Reset Flag

The CPU reset flag is set by hardware if software writes CPURST (SYS_IPRST0[1]) 1 to

reset Cortex

®

-M4 Core and Flash Memory Controller (FMC).

0 = No reset from CPU.

1 = The Cortex

®

-M4 Core and FMC are reset by software setting CPURST to 1.

Note:

Write 1 to clear this bit to 0.

[6]

PMURF

PMU Reset Flag

0 = No reset from POR, PINR, WDTR, LVR, BODR, SYSR and CPULKR.

1 = When POR, PINR, WDTR, LVR, BODR, SYSR and CPULKR occurred.

Note:

Write 1 to clear this bit to 0.

[5]

SYSRF

System Reset Flag

The system reset flag is set by the “Reset Signal” from the Cortex

®

-M4 Core to indicate the

previous reset source.

0 = No reset from Cortex

®

-M4.

1 = The Cortex

®

-M4 had issued the reset signal to reset the system by writing 1 to the bit

SYSRESETREQ(AIRCR[2], Application Interrupt and Reset Control Register, address =

0xE000ED0C) in system control registers of Cortex

®

-M4 core.

Note:

Write 1 to clear this bit to 0.