ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

535

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

1100

768

768 * 64 * T

WWDT

4.9152 s

1101

1024

1024 * 64 * T

WWDT

6.5536 s

1110

1536

1536 * 64 * T

WWDT

9.8304 s

1111

2048

2048 * 64 * T

WWDT

13.1072 s

Table 6.10.5-1 WWDT Prescaler Value Selection

6.10.5.1 WWDT Counting

When the WWDTEN (WWDT_CTL[0]) is set, WWDT down counter will start counting from 0x3F to

0. To prevent program runs to disable WWDT counter counting unexpected, the WWDT_CTL

register can only be written once after chip is powered on or reset. User cannot disable WWDT

counter counting (WWDTEN), change counter prescale period (PSCSEL) or change window

compare value (CMPDAT) while WWDTEN (WWDT_CTL[0]) has been enabled by user unless chip

is reset.

To avoid the system is reset while CPU clock is disabled, the WWDT counter will stop counting

when CPU enters Idle/Power-down mode. After CPU enters normal mode, the WWDT counter will

start down counting.

6.10.5.2 WWDT Compare Match Interrupt

During down counting by the WWDT counter, the WWDTIF (WWDT_STATUS[0]) is set to 1 while

the WWDT counter value (CNTDAT) is equal to window compare value (CMPDAT) and WWDTIF

can be cleared by user; if INTEN (WWDT_CTL[1]) is also set to 1 by user, the WWDT compare

match interrupt signal is generated also while WWDTIF is set to 1 by hardware.

6.10.5.3 WWDT Reset System

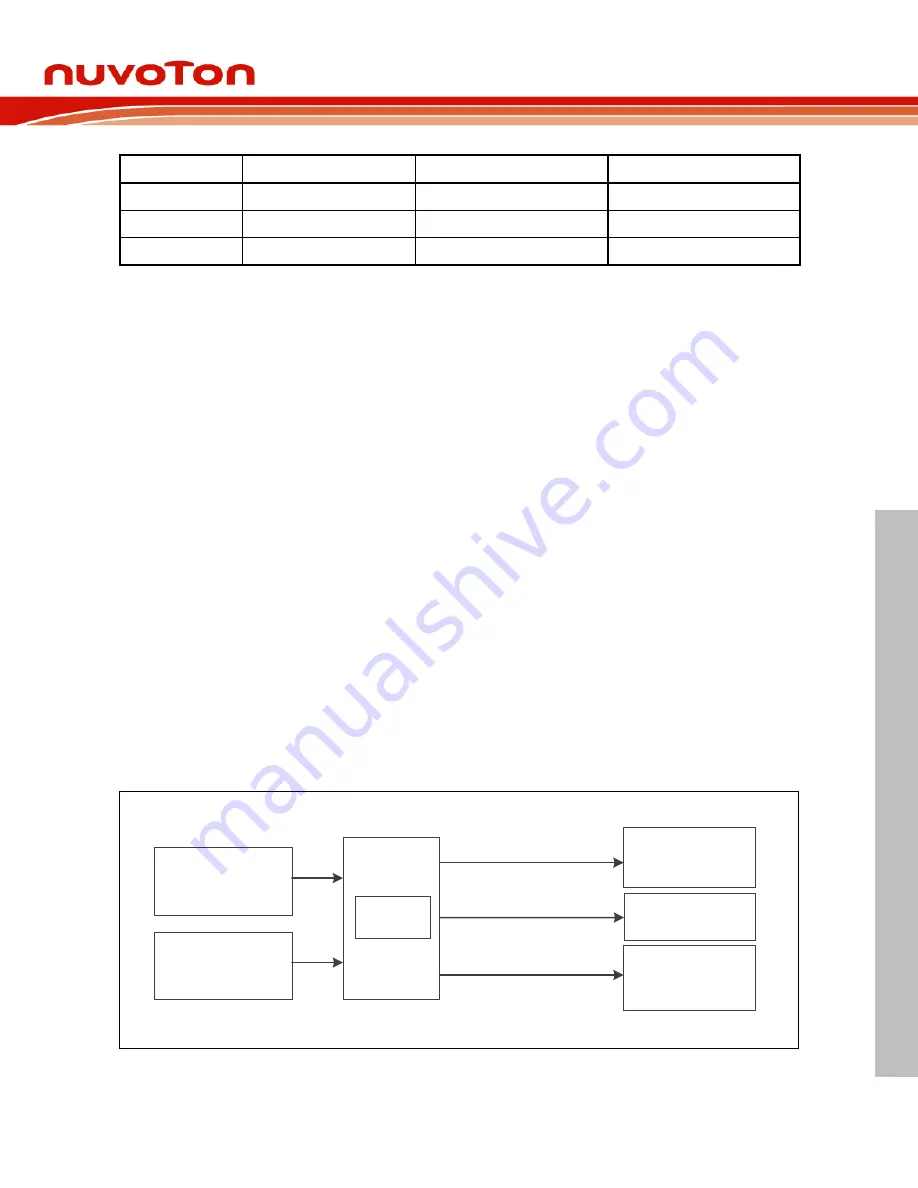

Figure 6.10-3 shows three cases of WWDT reset and reload behavior.

Comparator

6-bit compare value

CMPDAT

6-bit down counter

value CNTDAT

from 0x3F to 0x00

Write RLDCNT

0x5AA5 will

reset system

Write RLDCNT

0x5AA5 will

reload CNTDAT

to 0x3F

CNTDAT <= CMPDAT

System reset

immediately

CNTDAT = 0

CNTDAT > CMPDAT

Figure 6.10-3 WWDT Reset and Reload Behavior