ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

70

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

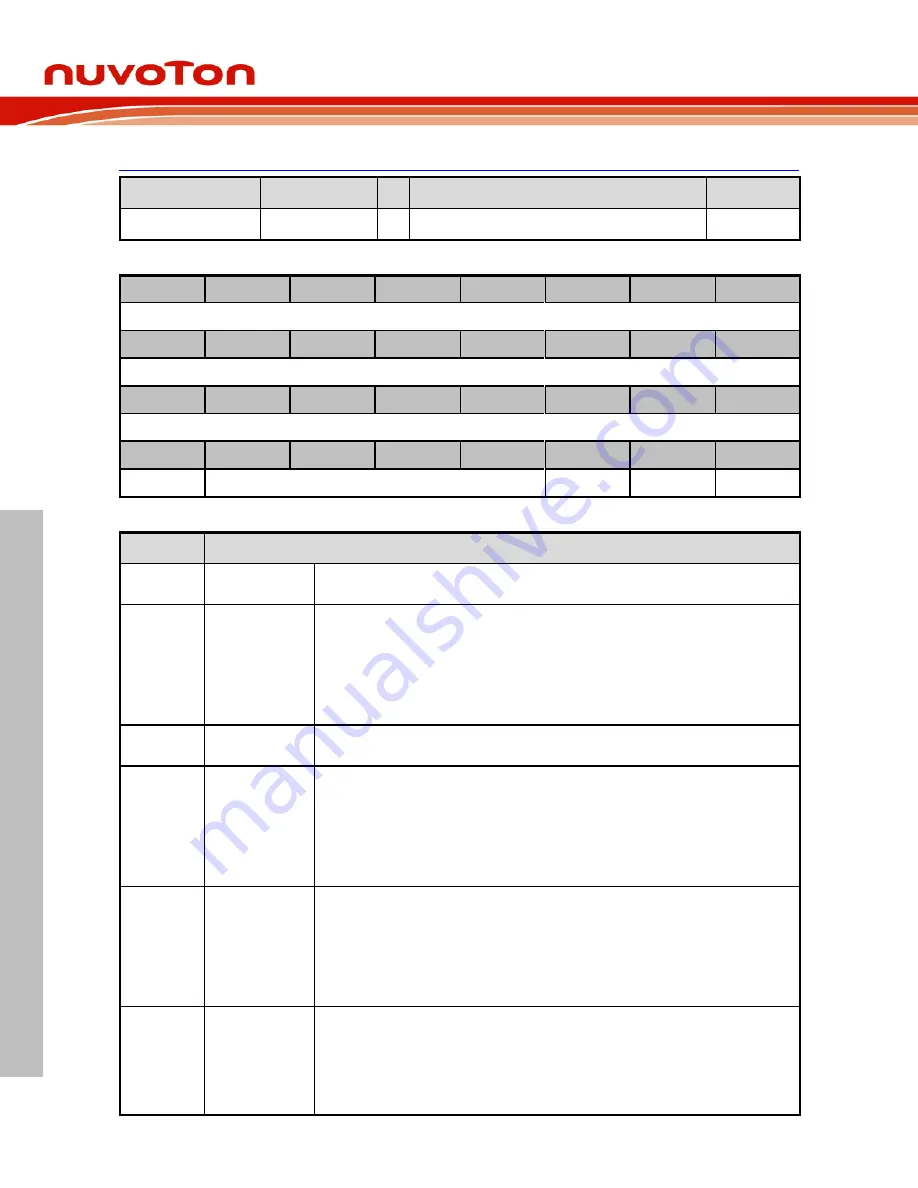

Peripheral Reset Control Register 0 (SYS_IPRST0)

Register

Offset

R/W Description

Reset Value

SYS_IPRST0

0x08

R/W Peripheral Reset Control Register 0

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

CRCRST

Reserved

PDMARST

CPURST

CHIPRST

Bits

Description

[31: 8]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[7]

CRCRST

CRC Calculation Controller Reset (Write Protected)

Set this bit to 1 will generate a reset signal to the CRC calculation controller. User needs to

set this bit to 0 to release from the reset state.

0 = CRC calculation controller normal operation.

1 = CRC calculation controller reset.

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.

[6:3]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[2]

PDMARST

PDMA Controller Reset (Write Protected)

Setting this bit to 1 will generate a reset signal to the PDMA. User needs to set this bit to 0

to release from reset state.

0 = PDMA controller normal operation.

1 = PDMA controller reset.

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.

[1]

CPURST

Processor Core One-shot Reset (Write Protected)

Setting this bit will only reset the processor core and Flash Memory Controller(FMC); this

bit will automatically return to 0 after the 2 clock cycles.

0 = Processor core normal operation.

1 = Processor core one-shot reset.

Note:

This bit is write protected. Refer to the SYS_REGLCTL register.

[0]

CHIPRST

Chip One-shot Reset (Write Protected)

Setting this bit will reset the whole chip, including Processor core and all peripherals; this

bit will automatically return to 0 after the 2 clock cycles.

The CHIPRST is same as the POR reset, all the chip controllers are reset and the chip

settings from flash configuration are also reloaded.

About the difference between CHIPRST and SYSRESETREQ(AIRCR[2]), please refer to