ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

685

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

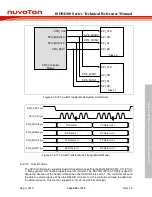

SPIx_SSy pin

TXEMPTY

(SPIn_STATUS[16])

SS1 and SS

(SPIn_SSCTL[1:0])

SPIx_CLK pin

One transaction

One transaction

The last

transaction

Note:

n, x: Controller number (x = 0, 1, 2), y: Slave selection pin channel number in SPI0 (y = 0, 1)

Figure 6.14-11 Automatic Slave Selection (SSACTPOL = 0, SUSPITV < 0x3)

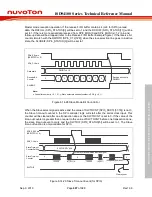

6.14.5.3 Byte Reorder and Suspend Function

When the transfer is set as MSB first (LSB = 0) and the REORDER (SPIn_CTL[19]) is set to 1, the

data stored in the TX buffer and RX buffer will be rearranged in the order as [Byte0, Byte1, Byte2,

Byte3] in 32-bit transfer (DWIDTH = 0). The sequence of transmitted/received data will be Byte0,

Byte1, Byte2, and then Byte3. If the DWIDTH is set as 24-bit transfer mode, the data in TX buffer

and RX buffer will be rearranged as [unknown byte, Byte0, Byte1, Byte2]. The SPI controller will

transmit/receive data with the sequence of Byte0, Byte1 and then Byte2. Each byte will be

transmitted/received with MSB first. The rule of 16-bit mode is the same as above. Byte Reorder

function is only available when DWIDTH is configured as 16, 24, and 32 bits.