ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

903

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

To configure the biquad filter and splitter:

Reset audio DPWM modulator by setting register

DPWMRST (SYS_IPRST2[6]).

Enable coefficient RAM programming mode by setting register

PRGCOEFF

(DPWM_COEFFCTL[0]) to “1”.

Set coefficients in coefficient registers, biquad coefficient is first, last 4 band coefficients are

for splitter.

Disable coefficient RAM programming mode by setting register

PRGCOEFF

(DPWM_COEFFCTL[0]) to “0”.

Set band number (biquad filter band 4 for Splitter) in register BIQBANDNUM

(DPWM_CTL[27:24]).

Enable biquad filter by setting register BIQON (DPWM_CTL[21]) to “1” and enable splitter by

setting register SPLTON (DPWM_CTL[22]) to “1”.

6.21.5.7 FIFO Data Operation

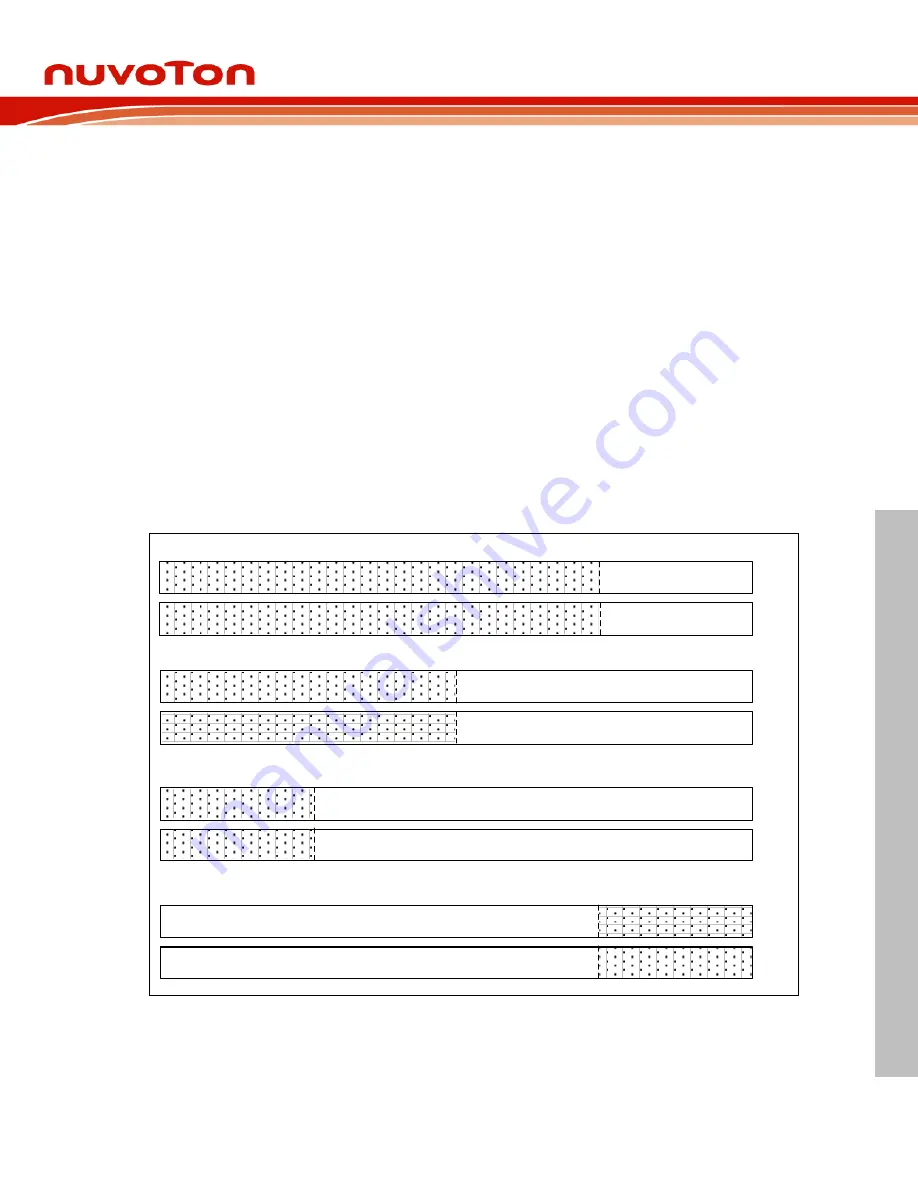

FIFO bits is 32 bits. It supports the single floating point and fixed point, channel position is as below.

The bit-width of audio data in a channel block can be 8, 16 or 24bits. The memory arrangements of

audio data for various settings are shown in Figure 6.21-4.

LEFT

RIGHT

N

N+1

0

0

FIFOWIDTH (DPWM_CTL[1:0]) = 11

23

23

LEFT

RIGHT

N

N+1

8

8

FIFOWIDTH (DPWM_CTL[1:0]) = 00

31

31

Redundant bits

Redundant bits

Redundant bits

Redundant bits

N

N+1

0

0

FIFOWIDTH (DPWM_CTL[1:0]) = 10

Redundant bits

Redundant bits

7

7

LEFT

RIGHT

N

N+1

0

0

FIFOWIDTH (DPWM_CTL[1:0]) = 01

Redundant bits

Redundant bits

15

15

LEFT

RIGHT

Figure 6.21-4 Audio DPWM FIFO Contents for Various Data Width

If it is fixed point set register FLTEN (DPWM_CTL[20]) to 0 and set FIFOWIDTH (DPWM_CTL[1:0])

for format. If it is the single floating point set FLTEN (DPWM_CTL[20]) to 1 and internal transfer it

to fixed point. Set FLTINBIT (DPWM_CTL[19:17]) for integer format.