ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

836

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

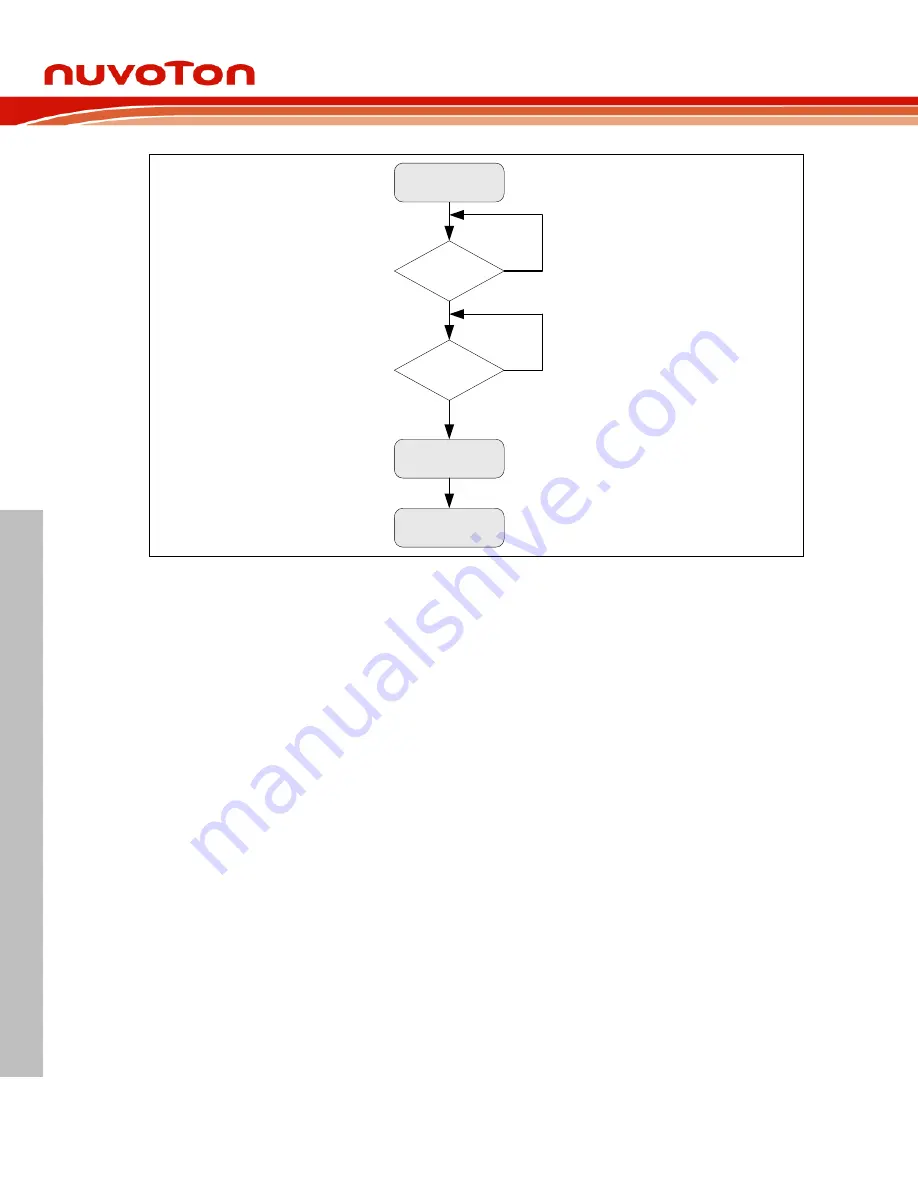

Wake Up Enable

System

Power Down

N

Y

System

Wake-up

N

Y

Wait 20ms

NEVWK Interrupt

Figure 6.18-2 NEVWK Interrupt Operation Flow

The USB interrupt is used to notify users of any USB event on the bus, and user can read EPSTS

(USBD_EPSTS0 and USBD_EPSTS1) and EPEVT11~0 (USBD_INTSTS[27:16]) to take

necessary responses.

Same as USB interrupt, BUS interrupt notifies users of some bus events, like USB reset, suspend,

time-out, and resume. User can read USBD_ATTR to acknowledge bus events.

6.18.5.6 Power Saving

User can write 0 to USBD_ATTR[4] to disable PHY under special circumstances, like suspend, to

conserve power.

6.18.5.7

Buffer Control

There is 1Kbytes SRAM in the controller and the 12 endpoints share this buffer. User shall configure

each endpoint’s effective starting address in the buffer segmentation register before the USB

function active. The “Buffer Control” block is used to control each endpoint’s effective starting

address and its SRAM size is defined in the USBD_MXPLDx register.

Figure 6.18-3 depicts the starting address for each endpoint according the content of

USBD_BUFSEGx and USBD_MXPLDx registers. If the USBD_BUFSEG0 is programmed as 0x08h

and USBD_MXPLD0 is set as 0x40h, the SRAM size of endpoint 0 is start from 0x108h

and end in 0x148h. (

Note:

The USBD SRAM base is 0x100h).